# 110 THYRISTOR PROJECTS using SCRs and TRIACS

R.M. Marston

110 Thyristor Projects using S.C.R.s and Triacs

# Other Books by R.M. Marston

20 Solid State Projects for the Home 20 Solid State Projects for the Car and Garage 110 Semiconductor Projects for the Home Constructor 110 Integrated Circuit Projects for the Home Constructor

# 110 Thyristor Projects using S.C.R.s and Triacs

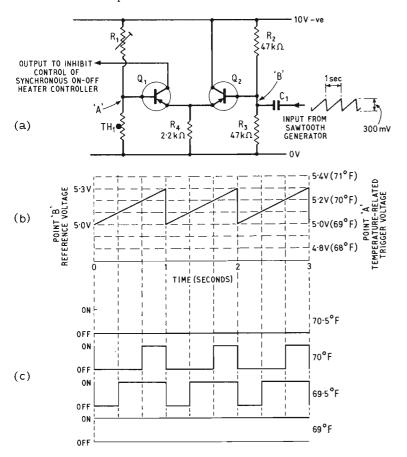

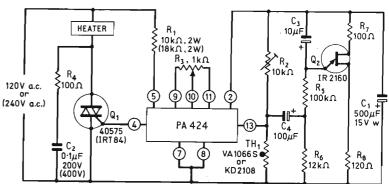

R.M. MARSTON

**Newnes Technical Books**

#### THE BUTTERWORTH GROUP

ENGLAND: Butterworth & Co (Publishers) Ltd

London: 88 Kingsway, WC2B 6AB

AUSTRALIA: Butterworths Pty Ltd

Sydney: 586 Pacific Highway Chatswood, NSW 2067

Melbourne: 343 Little Collins Street, 3000

Brisbane: 240 Queen Street, 4000

CANADA: Butterworth & Co (Canada) Ltd

Scarborough: 2265 Midland Avenue, Ontario M1P 4S1

NEW ZEALAND: Butterworths of New Zealand Ltd

Wellington: 26-28 Waring Taylor Street, 1

SOUTH AFRICA: Butterworth & Co (South Africa) (Pty) Ltd

Durban: 152-154 Gale Street

First published in 1972 by Newnes Technical Books Second impression 1975

© R. M. Marston, 1972

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, including photocopying and recording, without the written permission of the copyright holder, application for which should be addressed to the publisher. Such written permission must also be obtained before any part of this publication is stored in a retrieval system of any nature.

This book is sold subject to the Standard Conditions of Sale of Net Books and may not be sold in the U.K. below the net price given by the publishers in their current price list.

ISBN 0 592 00074 5 Limp

Printed in England by Billing & Sons Limited, Guildford and London

# **PREFACE**

S.C.R.s and triacs are high-speed solid-state power switches. They can operate at potentials up to hundreds of volts, and can handle currents up to tens or hundreds of amps. They have a multitude of applications in the home and in industry, and can readily be used to control electric lamps, motors, heaters and alarms.

This book is intended to be of equal interest to the electronics amateur, student and engineer. With this aim in mind, the volume starts off by outlining the essential operating characteristics of the s.c.r. and the triac, and then goes on to show 110 useful projects in which these devices can be used. All of these projects have been designed, built and fully evaluated by the author, and range from simple electronic alarms to highly sophisticated self-regulating electric-heater power controllers. Many of the projects use advanced design concepts, and are of outstanding technical interest. The operating principle of each project is explained in concise but comprehensive terms, and brief constructional notes are given where necessary.

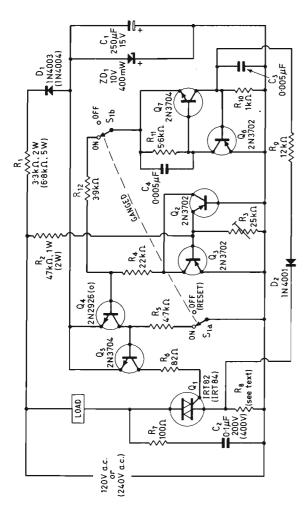

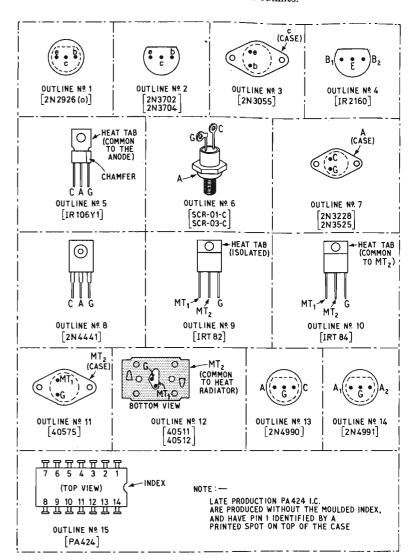

All of the projects are designed around internationally available components. The semiconductors used are of American manufacture, but are readily available in all parts of the western world. The volume is specifically designed to be of equal interest to both American and English readers. Where applicable, alternative component values are given for use on both 120 V and 240 V power lines, the 240 V values being noted in parentheses in the appropriate circuit diagrams. The outlines of all semiconductors used in the projects are given in the appendix, as an aid to construction. Unless otherwise stated, all resistors used in the projects are standard half-watt types.

# **CONTENTS**

| 1 | Basic Principles and Projects       | 1   |

|---|-------------------------------------|-----|

| 2 | 15 A.C. Power-Switching Projects    | 23  |

| 3 | 20 Electronic Alarm Projects        | 38  |

| 4 | 15 Time-Delay Projects              | 54  |

| 5 | 25 Lamp-Control Projects            | 68  |

| 6 | 15 Heater-Control Projects          | 94  |

| 7 | 15 Universal-Motor Control Projects | 110 |

| 8 | 5 Miscellaneous Projects            | 123 |

|   | Appendix                            | 132 |

|   | Index                               | 135 |

# BASIC PRINCIPLES AND PROJECTS

S.C.R.s and triacs are members of the thyristor family. They act as high-speed power switches. They are solid-state devices, and can operate at potentials up to several hundred volts, and can handle currents up to tens or hundreds of amps. They can be used to replace conventional mechanical switches and relays in many d.c. and a.c. power control systems, and can readily be used to control electric lamps, motors, heaters and alarms. They have a multitude of uses in the home and in industry.

This chapter explains the basic characteristics of these outstandingly useful devices, and shows a selection of basic circuits in which they can be used for demonstration and educational purposes.

# The s.c.r.: basic theory

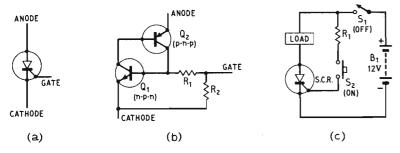

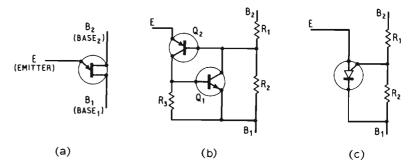

The s.c.r., or silicon controlled rectifier, is a four-layer pnpn silicon semiconductor device, and is represented by the symbol shown in *Figure 1.1a*. Note that this symbol resembles that of a normal rectifier, but has an additional terminal known as the 'gate'. The s.c.r. can be made to act as either an open-circuit switch or as a silicon rectifier, depending on how its gate is used.

Figure 1.1b shows the transistor equivalent circuit of the s.c.r. Essentially, the circuit is that of a complementary regenerative switch, in which the collector current of npn transistor  $Q_1$  feeds directly into the base of pnp transistor  $Q_2$  and the collector current of  $Q_2$  feeds into the base of  $Q_1$ . This equivalent circuit is of great value in understanding s.c.r. characteristics.

Figure 1.1c shows the basic connections for using the s.c.r. as a switch in d.c. circuits. The load is connected in series with the s.c.r. anode and cathode and is connected across the supply so that the anode

Figure 1.1a S.C.R. symbol.

Figure 1.1b Transistor equivalent circuit of the s.c.r.

Figure 1.1c Basic connections for using the s.c.r. as a d.c. switch.

is positive relative to the cathode. The gate can be connected to the positive supply line via  $R_1$  and  $S_2$ .

The basic characteristics of the s.c.r. can be readily understood by referring to *Figures 1.1b* and *1.1c*, and are as follows.

- (1). When power is first applied to the s.c.r. (by closing  $S_1$  in Figure 1.1c) the s.c.r. is 'blocked', and acts (between anode and cathode) like an open-circuit switch. Looking at Figure 1.1b it can be seen that this action is due to the fact that  $Q_1$  base is shorted to the cathode via  $R_1$  and  $R_2$ , so  $Q_1$  is cut off and passes negligible collector current into the base of  $Q_2$ , which is hence also cut off and passes negligible current into  $Q_1$  base. Both transistors are thus cut off under this condition, and only a small leakage current flows between the anode and cathode of the device.

- (2). The s.c.r. can be turned on and made to act like a normal silicon rectifier by applying a positive current to the gate by closing  $S_2$ . When this gate current is applied the s.c.r. regenerates and turns on very rapidly, and the full load current flows between the anode and cathode. As in the case of a normal silicon rectifier, a saturation potential of one or two volts is developed between the anode and cathode of the s.c.r. when it is on. Referring to Figure 1.1b, these characteristics can be explained as follows.

When the gate is made positive with respect to the cathode, gate current flows via  $R_2$  and via  $R_1$  and the base-emitter junction of  $Q_1$ . If the gate current is sufficiently large  $Q_1$  is biased on and its collector current feeds into the base of  $Q_2$ . This base current is amplified by  $Q_2$

and is fed back into the base of  $Q_1$ , where it is again amplified and fed to  $Q_2$ . A regenerative action thus takes place, and both transistors switch rapidly into saturation. Under this condition the anode-to-cathode saturation voltage is equal to the sum of the  $Q_2$  saturation voltage and the  $Q_1$  forward base-emitter voltage, and amounts to one or two volts. Modern s.c.r.s have typical turn-on times of a few microseconds.

(3). Once the s.c.r. has been turned on and is conducting in the forward direction the gate loses control, and the s.c.r. then remains on even if the gate drive is completely removed. Thus, only a brief positive gate pulse is needed to turn the s.c.r. on. Considerable current gain is available between the gate and anode of the device, so very small amounts of gate power can be used to control very high power values in the external load.

The above points should be self-evident from Figure 1.1b. A small drive current must be fed into the base of  $Q_1$  via  $R_1$  and the gate terminal to cause the circuit to regenerate initially, but once regeneration is complete the  $Q_1$  base drive necessary to sustain the circuit in the saturated state is provided via  $Q_2$  collector, so the circuit self-latches and remains on even when the gate drive is removed.  $R_1$  ensures that base current continues to flow in  $Q_1$  even if the gate-cathode terminals are shorted or reverse biased, so the gate loses all control once the circuit has switched into the self-latching mode.

Since  $Q_1$  and  $Q_2$  are connected as a positive feedback network they produce a combined loop gain equal to the product of their individual gains. Typically, s.c.r.s give current gains, between gate and anode, of the order of one thousand times. Milliamps of gate current can be used to control amps of anode current. The gate of the s.c.r. has non-linear characteristics similar to those of the base of a normal silicon transistor (as is self-evident from Figure 1.1b), and gate potentials of the order of one volt are sufficient to turn the s.c.r. on. S.c.r.s can be used to switch potentials up to several hundred volts, so high voltage gains are available from the device. Thus, extremely high power (volts x amps) gains are available from s.c.r.s, and milliwatts of gate power can be used to control kilowatts of load power.

(4). Once the s.c.r. has self-latched into the on state it can only be turned off again by momentarily reducing its anode current to zero, or below a value known as the 'minimum holding current'. Since turn-off occurs whenever the current is reduced below this critical value, it follows that turn-off occurs automatically in a.c. circuits near the zero-crossing point at the end of each half-cycle. The fact that turn-off occurs when the main current falls below a minimum holding value, rather than to zero, is due to the fact that the current gains of the two transistors in the *Figure 1.1b* circuit fall off as the anode current is

#### 4 BASIC PRINCIPLES AND PROJECTS

reduced, and the circuit unlatches when the anode current falls to such a low value that the combined loop gain of the two transistors falls below unity. Minimum holding current values are typically of the order of a few milliamps.

(5). A certain amount of internal capacitance exists between the anode and gate of the s.c.r. Consequently, if a sharply rising voltage is applied to the s.c.r.s anode this internal capacitance can cause part of the rising anode signal to break through to the gate and thus trigger the s.c.r. on. This 'rate-effect' turn-on can be caused by supply-line transients, and sometimes occurs at the moment that supplies are switch-connected to the s.c.r. anode. Rate-effect problems can usually be overcome by wiring a simple R-C smoothing network between the anode and cathode of the s.c.r., to limit the rate of rise to a safe value.

#### The s.c.r.: basic d.c. circuits

Having examined the basic characteristics of the s.c.r. we can now go on to look at a few basic circuits that can be used to demonstrate these characteristics in a practical way.

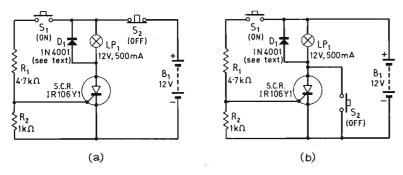

Figure 1.2a shows a simple d.c. on-off circuit controlling a 12 V 500 mA lamp. The lamp can be replaced with an alternative type of

Figure 1.2a Simple d.c. on-off circuit. Figure 1.2b Alternative d.c. on-off circuit.

load if required, but if an inductive load is used it must be shunted by a damping diode  $(D_1)$ , so that the circuit is not damaged by back e.m.f.s as the s.c.r. is switched on or off. The s.c.r. used here can handle anode currents up to 2 A, and can be turned on by gate currents as low as a few hundred microamps. Gate current is provided via limiting resistor  $R_1$ and push-button switch  $S_1$ .  $R_2$  is wired between the s.c.r.s gate and cathode to improve circuit stability, in the same way as a resistor may

be wired between the base and emitter of a conventional transistor for the same purpose.

The Figure 1.2a circuit can be turned on by briefly closing  $S_1$ . Once the circuit has been turned on it self-latches and stays on when  $S_1$  is opened again. The circuit can be turned off by momentarily reducing the anode current to zero by opening  $S_2$ . Alternatively, the circuit can be turned off by momentarily applying a short between the s.c.r.s anode and cathode, as shown in Figure 1.2b.

Figure 1.3 shows a third way of achieving s.c.r. turn-off. Here, once the s.c.r. has been turned on,  $C_1$  charges up via  $R_3$  and the s.c.r. to

Figure 1.3. Capacitor-turn-off circuit.

almost the full supply line potential, the  $R_3$  end going positive. When  $S_2$  is operated the positive end of  $C_1$  is clamped to ground, and the capacitor charge forces the s.c.r. anode to momentarily swing negative, thereby reverse-biasing the s.c.r. and causing it to turn off. The capacitor charge leaks away rapidly under this condition, but has to hold the s.c.r. anode negative for only a few microseconds to ensure complete turn-off. Note that if  $S_1$  is held down after the charge has leaked away, the capacitor then starts to charge in the reverse direction

Figure 1.14. Capacitor-turn-off circuit with s.c.r. slaving.

via the lamp load:  $C_1$  must thus be a non-polarised type, such as Mylar or polyester.

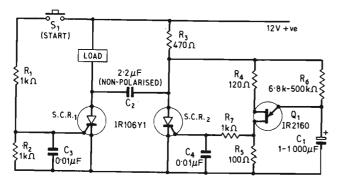

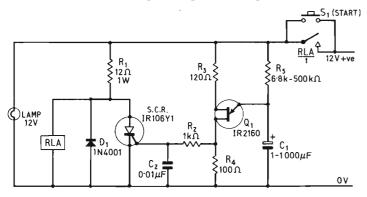

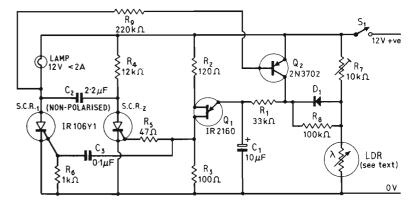

A variation of the capacitor turn-off circuit is shown in Figure 1.4. Here a slave s.c.r. is used to replace  $S_2$  of Figure 1.3, and capacitive turn-off of  $SCR_1$  is achieved by briefly driving  $SCR_2$  on via a low-current pulse from  $S_2$ .  $SCR_2$  turns off once  $S_2$  is released, since the anode current provided by  $R_3$  is lower than the  $SCR_2$  holding current.

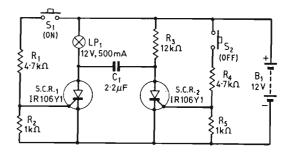

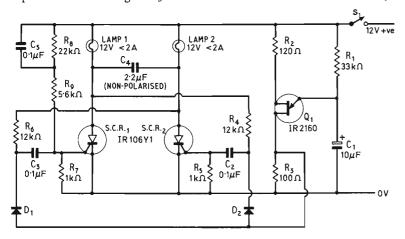

Figure 1.5 shows the circuit of an s.c.r. bistable or flip-flop driving two independent lamp loads. Assume that  $SCR_1$  is on and  $SCR_2$  is off,

Figure 1.5. S.C.R. bistable or flip-flop.

so that  $C_1$  (non-polarised) is fully charged with its  $LP_2$  end positive. The state of the circuit can be changed by momentarily operating  $S_2$ .  $SCR_2$  is then driven on via its gate, and as it goes on it drives  $SCR_1$  off capacitively via its anode.  $C_1$  then recharges in the reverse direction. Once recharging is complete the state of the circuit can again be changed by briefly operating  $S_1$ , thus driving  $SCR_1$  on via its gate and driving  $SCR_2$  off capacitively via its anode. The flip-flop process can be repeated ad infinitum.

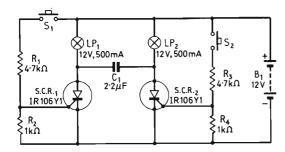

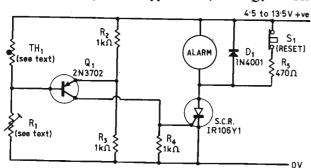

All the d.c. circuits that we have looked at so far have used simple fixed loads, and have thus been of the self-latching type. Figure 1.6a, however, shows a simple d.c. alarm circuit driving a self-interrupting load such as a bell, buzzer, or siren. When self-interrupting devices such as these are connected across a supply a current flows through a built-in solenoid via a pair of contacts; this current induces a magnetic field in the solenoid, and causes a striker to fly outwards and open the contacts, causing the current to fall to zero and making the magnetic field collapse. Once the field has collapsed the striker falls back again and the contacts close, so current is again applied to the solenoid and the action repeats.

Consequently, this type of load acts like a switch that repetitively opens and closes rather rapidly. When such loads are connected in the *Figure 1.6a* circuit, therefore, the circuit does not self-latch in the

normal way, and the alarm operates only so long as  $S_1$  is closed. Due to the inductive nature of such loads a damping diode must be wired across them when they are used in s.c.r. circuits, as shown in the diagram.

The alarm circuits can be made to self-latch, if required, by simply wiring a 470-ohm resistor in parallel with the alarm, as shown in

Figure 1.6a. Simple non-latching

Figure 1.6b. Simple self-latching alarm circuit.

Figure 1.6b. In this case the anode current of the s.c.r. does not fall to zero when the alarm self-interrupts, but falls to a value dictated by  $R_3$  and the battery voltage. If this current is in excess of the s.c.r.s holding current the s.c.r. self-latches. The circuit can be unlatched by briefly operating  $S_2$ , so that the anode current falls to zero when the alarm enters a self-interrupting stage, and the s.c.r. turns off.

The actual alarm used in the *Figure 1.6* circuits can be any low-voltage (3 to 12 V) self-interrupting bell, buzzer, or siren that draws an operating current of less than 2 A. The supply battery should give a voltage roughly 1.5 V greater than the normal operating voltage of the alarm device, to compensate for the saturation voltage that is 'lost' across the s.c.r. when it is on.

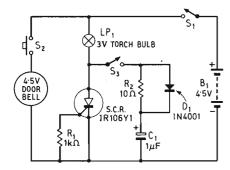

Figure 1.7 shows a circuit that can be used to demonstrate the rate-effect turn-on of the s.c.r., and a method that can be used for rate-effect suppression. Here, the s.c.r. uses a 3 V lamp as its anode load, and is connected across the 4.5 V battery supply via  $S_1$ . A 4.5 V domestic door bell can be connected across the supply via  $S_2$ , and enables transient modulation to be applied to the supply line and thus to the anode of the s.c.r. This modulation can cause rate-effect turn-on of the IR106Y1 s.c.r., which has a critical rate-of-rise value of  $20 \text{ V/}\mu\text{s}$ .

To demonstrate the rate-effect, open  $S_3$  so that the suppressor network is removed from the s.c.r., connect the supply by closing  $S_1$ , and then close  $S_2$  so that the bell rings. As the bell operates it applies

#### 8 RASIC PRINCIPLES AND PROJECTS

high transient modulation to the positive supply line, and this modulation appears at the s.c.r. anode and should trigger the s.c.r. and the lamp on. If the lamp does not go on, it may be that the battery has a low internal resistance. If so, try connecting a 0.5-ohm resistor in series with

Figure 1.7. Rate-effect demonstration circuit.

the battery, so that the correct operation is obtained. Once the s.c.r. and lamp have been triggered on by rate-effect they can be turned off again by briefly opening  $S_1$ .

Once the turn-on rate-effect has been demonstrated the effects of the suppressor network can be shown by closing  $S_3$  and operating the bell again via  $S_2$ . When  $S_3$  is closed the lamp resistance and  $C_1$  act as a smoothing network that reduces the rate-of-rise of the anode modulation signal to a safe value, and the s.c.r. does not go on when the bell operates. If the s.c.r. still goes on under this condition, increase the  $C_1$ value until the correct results are obtained.  $C_1$  charges to the full supply line potential when  $S_1$  is closed, and  $R_2$  is wired in series with  $C_1$  to limit its discharge current into the s.c.r. anode to a safe value.  $D_1$  makes  $R_2$  appear as a virtual short-circuit to sharply rising anode signals, however, so  $R_2$  does not effect the time constant of the R-C rate-effect suppression network formed by  $C_1$  and the lamp resistance. In many applications  $D_1$  can be eliminated from the suppressor circuit.

#### The s.c.r.: basic a.c. circuits

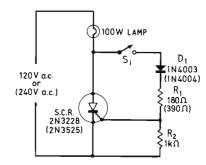

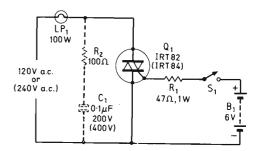

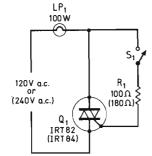

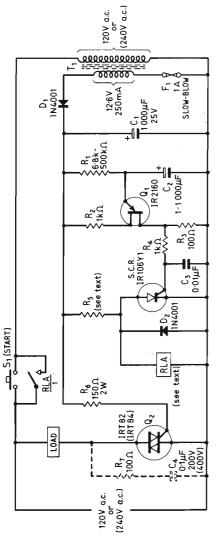

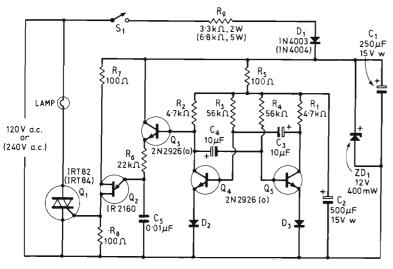

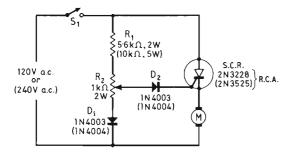

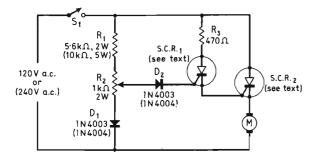

Figure 1.8 shows a basic half-wave a.c. on-off circuit driving a 100 W lamp from a 120 V or 240 V a.c. power line. With S<sub>1</sub> open zero drive is applied to the s.c.r. gate, so the s.c.r. and lamp are off. Suppose, however, that  $S_1$  is closed. At the start of each positive half-cycle the s.c.r. is off, so the full available line voltage is applied to the gate via the lamp and  $D_1$  and  $R_1$ . Shortly after the start of the half-cycle sufficient voltage is

available to trigger the s.c.r., and the s.c.r. and lamp go on. As the s.c.r goes on its anode voltage falls to near zero, thus removing the gate drive current. Since a substantial anode current is flowing in the s.c.r. at this time, however, the s.c.r. remains fully latched on for the duration of the half-cycle. The s.c.r. automatically turns off when the half-cycle ends and the anode current falls to zero.

This process repeats, with the s.c.r. triggering on shortly after the start of each positive half-cycle, so long as  $S_1$  is closed, and half-wave

Figure 1.8. Line-driven half-wave on-off circuit.

power is applied to the lamp. The s.c.r. and lamp turn off when  $S_1$  is re-opened, since s.c.r. turn-off occurs automatically at the end of each positive half-cycle.

Diode  $D_1$  in this circuit prevents reverse bias being applied to the s.c.r. gate on negative half-cycles of line voltage.  $R_1$  is given a low value so that the s.c.r. can be turned on as early as possible in each positive half-cycle, but is large enough to limit the peak gate current to a safe value in the event of  $S_1$  first being closed when the instantaneous line voltage is at its peak value. Note that although very high peak voltage and and current values may be applied to  $R_1$ , they are applied for only the few microseconds that the s.c.r. takes to turn on; the mean power dissipation of  $R_1$  is thus quite low, and this component can safely be given a half-watt rating.

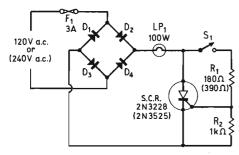

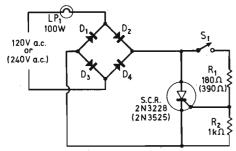

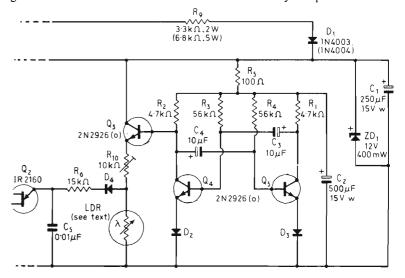

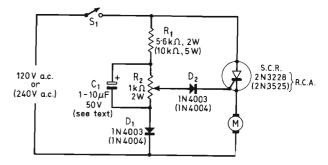

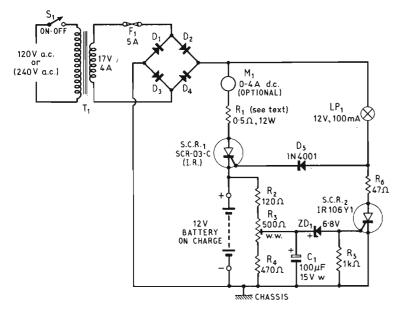

S.C.R.s can be used in a variety of ways to give full-wave a.c. control. In Figures 1.9 and 1.10 the a.c. is converted to rough (unsmoothed) d.c. via the bridge rectifier  $D_1 - D_4$ , and the rough d.c. is applied to the s.c.r. With  $S_1$  open the s.c.r. is off, so zero current flows through the bridge and the load. When  $S_1$  is closed the s.c.r is driven on shortly after the start of each half-cycle of rough d.c., and full-wave power is applied to the load. As the s.c.r. goes on in each half-cycle the gate drive is automatically removed, but the s.c.r. stays latched on for the duration of each half-cycle, as already described. The s.c.r. switches off

#### BASIC PRINCIPLES AND PROJECTS

automatically at the end of each half-cycle as its anode current falls to zero, so power is automatically removed from the load when  $S_1$  is opened.

Note in the Figure 1.9 circuit that the load is connected in the d.c. side of the bridge, and the circuit is thus used to drive a d.c. load. A fuse

Figure 1.9. Full-wave on-off circuit with a d.c. load.  $D_1 - D_A = 3A$  200 p.i.v. silicon rectifiers. (3A 400 p.i.v. silicon rectifiers.)

is placed in the a.c. side of the bridge to give protection in the event of a failure of one or more of the bridge components. In the Figure 1.10 circuit the load is placed in the a.c. side of the bridge, so the circuit is used to control an a.c. load. A fuse is not required in this case, since the load itself limits current to a safe value in the event of a component failure.

Figure 1.10. Full-wave on-off circuit with a.c. load.  $D_1 - D_4 = 3A$  200 p.i.v. silicon rectifiers. (3A 400 p.i.v. silicon rectifiers.)

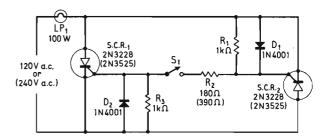

Finally, Figure 1.11 shows how two s.c.r.s can be connected in inverse parallel to give direct full-wave switching of the load. With  $S_1$ open zero gate drive is applied to either s.c.r., so zero power is applied to the load. When  $S_1$  is closed gate current is applied to  $SCR_1$  on positive half-cycles via  $D_1$  and  $R_2$ , and  $SCR_1$  is driven on. On negative

Figure 1.11. Full-wave line switch using two s.c.r.s.

half-cycles gate drive is applied to  $SCR_2$  via  $D_2$  and  $R_2$ , and  $SCR_2$  is driven on. Full-wave control is thus obtained.

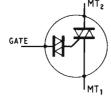

# The triac: basic principles and projects

S.C.R.s are unidirectional thyristor devices. They pass current in one direction only, from anode to cathode. Triacs are also members of the thyristor family, but are bidirectional devices. They can pass current in either direction. For most practical purposes a triac can be regarded as two conventional s.c.r.s connected in inverse parallel within a single three-terminal package, but so arranged that the two s.c.r.s share a single gate terminal. The triac can be used as a solid-state power switch that is normally off but can be turned on via a suitable gate signal.

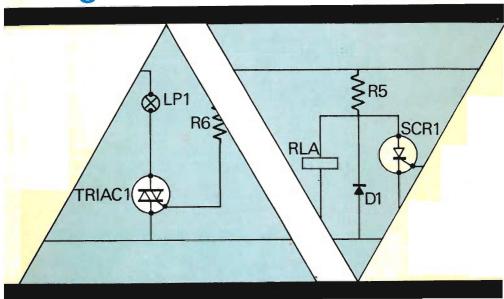

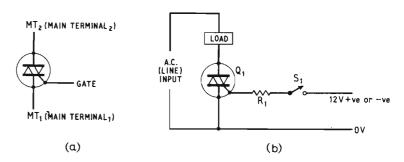

Figure 1.12a shows the symbol that is used to represent the triac, and Figure 1,12b shows a basic connection for using the device as an a.c. power switch. The load is wired in series with the triacs main

Figure 1.12a. Triac symbol. Figure 1.12b. Basic triac switching circuit with d.c. gate drive.

terminals, and the series combination is wired directly across the a.c. power line: D.C. gate drive can be applied to the triac by closing  $S_1$ .

The triac exhibits characteristics very similar to those of a pair of s.c.r.s connected in inverse parallel. Referring to Figure 1.12b, these characteristics are as follows.

- (1). Normally, with no gate signal applied, the triac is off and acts (between  $MT_1$  and  $MT_2$ ) like an open-circuit switch. It passes negligible current in either direction, and zero power is applied to the load.

- (2). If  $MT_2$  is appreciably positive or negative relative to  $MT_1$  the triac can be turned on (so it acts like a closed switch between  $MT_1$  and  $MT_2$ ) by applying a suitable trigger or bias signal to its gate via  $S_1$ . The device takes only a few microseconds to switch fully on.

- (3). Once the triac has been turned on via its gate it self-latches, and remains on so long as main-terminal currents continue to flow. Only a brief pulse of gate current is thus needed to turn the triac on.

- (4). Once the triac has self-latched the gate loses control and the device can only be turned off again by momentarily reducing its mainterminal currents below a near-zero minimum holding value. When the triac is used as an a.c. power switch, therefore, turn-off occurs automatically at the zero-crossing point at the end of each half-cycle as the main-terminal currents fall to zero.

- (5). A saturation potential of one or two volts is developed across the triacs main-terminals when the device is switched into the on state. Thus if the triac is used to switch a 10 A load from a 240 V r.m.s. supply, and the triac has a saturation potential of 1.5 V, approximately 2 400 W can be switched by the triac, but only 15 W are 'lost' in the triac itself: This 15 W can be readily dissipated by connecting the triac to a suitable heat sink. The triac thus makes an efficient a.c. power switch.

- (6). The triac can be turned on by either a positive or a negative gate signal, irrespective of the polarities of the main-terminal voltages. The device thus has four possible triggering modes, signified as follows:

$$I^{+}$$

Mode =  $MT_{2}$  current +ve, Gate current +ve.

$I^{-}$  Mode = " '+ve, " '-ve.

$III^{+}$  Mode = " '-ve, " '+ve.

$III^{-}$  Mode = " '-ve, " '-ve.

The gate sensitivities in the I<sup>+</sup> and III<sup>-</sup> modes are relatively high, and are approximately equal. The sensitivities in the I<sup>-</sup> and III<sup>+</sup> modes are also roughly equal to one another in modern triacs, but are only about half as great as in the I<sup>+</sup> and III<sup>-</sup> modes. The gate exhibits non-linear characteristics similar to those of the s.c.r. Gate potentials of one or two volts and currents of a few tens of milliamps are sufficient to turn on a triac and control several amps of load current. Considerable power gain is thus available between the triac gate and the load.

Having examined the basic characteristics of the triac we can now go on to look at a few basic switching circuits that can be used to demonstrate these characteristics in a practical way.

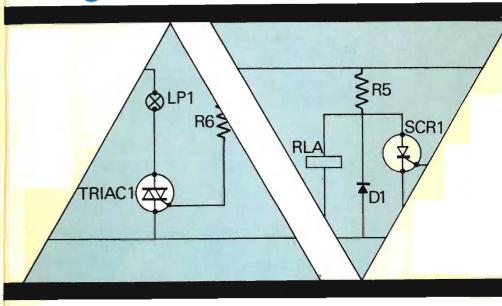

Figure 1.13 shows the practical circuit of a simple d.c. triggered triac power switch. When  $S_1$  is open zero current flows to the gate of the triac, which is thus off. Zero power is applied to the load under this condition. When  $S_1$  is closed gate drive is applied to the triac via  $R_1$  and the battery, and the triac is driven on and acts like a closed switch. Full power is thus applied to the load under this condition.

Figure 1.13. D.C.-triggered triac line switch.

Note in this circuit that positive gate drive is applied to the triac whenever  $S_1$  is closed, irrespective of the  $MT_2$  polarity. The triac is thus gated in the I<sup>+</sup> and III<sup>+</sup> modes alternately. The R<sub>1</sub> value is made low enough to trigger the triac even in the relatively insensitive III + mode.

The lamp load of the Figure 1.13 circuit can, if desired, be replaced with an alternative type of load. If an inductive load such as a motor is used, the  $R_2-C_1$  network must be wired in place as indicated. Alternating currents and voltages are inherently out of phase with one another in all inductive loads: When the triac turns off as its main-terminal current falls to zero in each half-cycle, therefore, these phase differences cause a high value of instantaneous line voltage to be suddenly applied to the triac: If the rate-of-rise of this 'commutation' or turn-off voltage exceeds a critical value it can trigger the triac back on again by rateeffect, so that the triac effectively stays permanently locked on. This problem can be overcome by wiring the  $R_2 - C_1$  rate-effect suppression or 'snubber' network across the triac to limit its rate-of-rise to a safe value of about  $1V/\mu_s$ .

Figure 1.14 shows how the triac can be used as a simple line switch with line-derived triggering. When  $S_1$  is open zero drive is applied to the triac gate, so the triac and lamp are off. Suppose, however, that  $S_1$  is closed. At the start of each half-cycle the triac is off, so the full line voltage is applied to the gate via the lamp and  $R_1$ . Shortly after the start

#### BASIC PRINCIPLES AND PROJECTS

of the half-cycle sufficient drive is available to trigger the triac, and the triac and lamp go on. As the triac goes on it saturates, thus removing the gate drive. Once it has turned on the triac self-latches and stays on until the end of the half-cycle, when it automatically turns off again as its main-terminal current falls to zero.

This process repeats, with the triac triggering on shortly after the start of each half-cycle, so long as  $S_1$  is closed, and full power is applied to the lamp. The triac and lamp turn off again when  $S_1$  is opened. Note

Figure 1.14. Line-triggered line switch.

in this circuit that the triggering occurs alternately in the sensitive I+ and III $^-$  modes.  $R_1$  is given a low value so that the triac is turned on as early as possible in each half-cycle, but the value is large enough to limit the peak gate current to a safe value if  $S_1$  is first closed at the moment when the instantaneous line voltage is at its peak value.

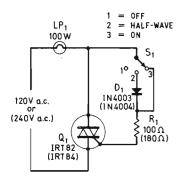

Finally, Figure 1.15 shows how the triac can be wired as a simple three-way line switch, giving Off-half-wave-On operation. When S<sub>1</sub> is in the '1' position zero drive is applied to the triac gate, so the triac

Figure 1.15. Three-way line switch.

and lamp are off. In position '2' gate drive is applied via  $D_1$  on positive half-cycles only, so the lamp is operated at half-wave power. In position '3' gate drive is applied on all half-cycles, and the circuit operates in the same way as Figure 1.14. Full power is applied to the lamp load.

# Phase-triggered power-control principles

The s.c.r. and triac circuits that we have looked at so far have all been used to give a simple on-off type of power control in which either full or zero power is applied to the load. S.C.R.s and triacs are, however, readily capable of giving fully variable control of a.c. loads, and can be used to infinitely and smoothly vary the load power all the way from zero to maximum. They are thus suitable for use in applications such as lamp dimmers, electric motor speed controllers, and electric heater power controllers.

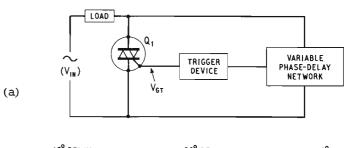

The most widely used system of s.c.r. and triac variable power control in a.c. circuits is known as the 'phase triggering' system. The principle is illustrated in Figure 1.16.

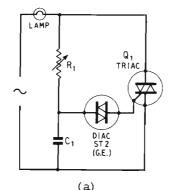

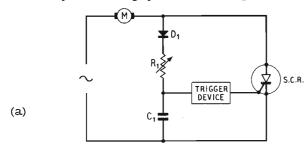

Figure 1.16a shows the basic phase-triggered circuit, using a triac as the power control element. The load is wired in series with the triac, and the combination is connected across the a.c. power line. The triac gatetrigger signal is derived from MT<sub>2</sub> via a variable phase-delay network and

Figure 1.16a. Basic phase-triggered variable power-control circuit. Figure 1.16b. Waveforms of the Figure 1.16a circuit at various phase-delay settings.

a trigger device. The phase-delay network enables the a.c. voltage to the input of the trigger device to be delayed relative to that on  $MT_2$  by an amount fully variable from (ideally) 0° to 180°, i.e., by as much as one half-cycle of line voltage.

The trigger device is a voltage-operated 'switch' that triggers on and fires the triac when a preset voltage is reached at the output of the phasedelay network, or at the end of the pre-set phase-delay period.

Figure 1.16b shows the waveforms that occur in different parts of the circuit at three different settings of phase delay. Thus, if the phase delay network is set for only a 10° delay the triac is triggered on 10° after the start of each half-cycle, and then self-latches and stays on for the remaining 170° of each half-cycle. Almost the full available line power is thus applied to the load under this condition.

If the circuit is set for a phase-delay of 90°, the triac does not turn on until half-way through each half-cycle, and only half of the maximum possible power is applied to the load. Finally, if the circuit is set for a 170° delay the triac does not turn on until 10° before the end of each half-cycle, and very little power is applied to the load under this condition. Thus, the load power can be varied all the way from zero to maximum by varying the setting of the phase-delay control. Since the triac is either fully off or is saturated at all times very little power is 'lost' in the device, and very efficient variable power control is obtained.

The actual phase-delay section of the Figure 1.16 circuit can take either of two basic forms. It can consist of either a single or multiple R-C variable phase-shift network, or of an R-C variable time-delay network that simulates a phase-delay by its time-equivalent: e.g., a half-cycle of 50 Hz line voltage has a period of 10 ms, giving a period of 55.5 µs per degree of phase delay; a 90° phase-triggered delay can thus be simulated by a time delay of 5 ms, etc.

The actual trigger device used in the circuit is usually some kind of solid-state switch, and can take any one of a number of forms. Basic details of a variety of trigger devices and special-purpose s.c.r.s and triacs are given in the final section of this chapter.

# Radio-frequency interference

S.C.R.s and triacs act as high-speed power switches. They have typical turn-on times of only a few microseconds. When they are used to switch power into a load these high switching speeds result in the generation of a series of harmonically related radio-frequency signals. The magnitude of the fundamental r.f. signal is proportional to the magnitude of the device switching current, and may be so great that it causes interference on a.m. radios.

Two basic types of radio-frequency interference (r.f.i.) may be generated by s.c.r.s and triacs when they are used in line-powered switching applications. One of these is radiated r.f.i. which is radiated directly into the air as a radio signal. In most cases this type of r.f.i. is of such low intensity that it does not cause significant interference with a.m. radios unless they are placed very close to the source of radiation. If radiated r.f.i. is troublesome, it can be minimised by mounting the thyristor circuitry in a screened container.

The second and more troublesome type of radio frequency interference is conducted r.f.i., which is carried through the power lines and may affect radio and TV sets connected to the same power lines. Trouble from this type of r.f.i. can be minimised by connecting a simple L-Cfilter in series with the power line, so that the conducted high-frequency harmonics of the basic switching signal are reduced to insignificant levels.

Looking back at some of the triac switching circuits described earlier. the following points should be noted concerning r.f.i.

In the Figure 1.13 circuit the triac is off when  $S_1$  is open, so no r.f.i. is generated. When  $S_1$  is closed the triac is permanently on, and does not perform a high-speed switching function, so zero r.f.i. is again generated. The triac does switch on rapidly at the instant that  $S_1$  is first closed, however, and thus generates a brief pulse of r.f.i. at that instant. The magnitude of this pulse is proportional to the magnitude of the instantaneous turn-on current, and thus line voltage, at the moment that  $S_1$  is closed, and may be of substantial proportions. Since the pulse is very brief and only occurs as  $S_1$  is operated, however, the resulting r.f.i. is unlikely to cause annoyance. This initial switch-on r.f.i. can only be completely eliminated by using a synchronous zero-voltage gating technique, in which gate drive can only be applied to the triac in the brief periods when the line voltage is at or near the zero-voltage cross-over point near the start of each half-cycle.

The Figure 1.14 circuit also generates a brief pulse of r.f.i. as  $S_1$ is closed, in the same way as described above. In addition, however, the circuit generates a continuous r.f.i. signal of low intensity while  $S_1$  is closed. This r.f.i. is caused by the fact that the triac does not turn on in each half-cycle until the line voltage has risen to a value (of a few volts) sufficient to trigger the device on via  $R_1$ , at which point the triac switches sharply into saturation. A switching pulse is thus generated shortly after the start of each half-cycle of line voltage so long as  $S_1$  is closed. This pulse is, however, of low intensity; and will not effect a.m. radios unless they are placed very close to the triac circuit.

Finally, consider the case of the phase-triggered variable power control circuit of Figure 1.16. This circuit also triggers on some time

after the start of each half-cycle, and thus generates continuous r.f.i. In this case, however, very high switching currents may be involved, particularly when the circuit is set for a 90° delay, and high levels of r.f.i. may thus be generated. This r.f.i. is predominantly of the conducted type, and must be suppressed if it is not to interfere with a.m. radios. If the circuit is used with an inductive load such as a motor, the inductance itself will act as an effective r.f.i. suppressor. If a resistive load such as a lamp is used, the circuit must be fitted with a simple L-C suppressor to filter out the higher harmonic signals.

#### Miscellaneous thyristors and trigger devices

S.C.R.s and triacs are two members of a wide range of solid-state devices in the thyristor family. In this final section of this chapter we shall take a brief look at the characteristics of six other members of the family, and at two special triggering devices that are associated with them, as follows.

The l.a.s.c.r. This device is simply a Light Activated s.c.r. All semiconductor junctions are sensitive to light, and most active semiconductor devices are consequently shrouded in an opaque material to exclude unwanted light effects. The l.a.s.c.r., however, is deliberately manufactured so that one or more of its junctions can be readily exposed to light, so that the s.c.r. can be directly triggered on by a light source.

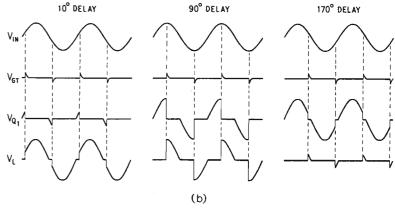

The s.c.s. The s.c.s., or Silicon Controlled Switch, uses the symbol shown in Figure 1.17a. Note that this symbol resembles that of a normal s.c.r., but has an additional gate terminal near its anode. Figure 1.17b shows the approximate equivalent circuit of the device. Note that this equivalent circuit is very similar to that of the s.c.r. shown in Figure 1.1b, except that the base of  $Q_2$  is available externally at the anode gate terminal. The characteristics of the device are in fact very similar to those of the s.c.r., with the following exceptions:

Figure 1.17a. S.C.S. symbol. Figure 1.17b. Approximate equivalent circuit of the s.c.s.

emitter junction of either  $Q_1$  or  $Q_2$  via the external gate terminals, i.e., the device can be turned on by applying a positive pulse to the cathode gate or by applying a negative pulse to the anode gate. (b) Once the device has turned on it can be turned off again by

The device can be turned on by forward biasing the base-

reverse biasing the base-emitter junction of either  $O_1$  or  $O_2$ , i.e., by applying a negative pulse to the cathode gate or a positive pulse to the anode gate.

This device is simply a Light Activated s.c.s., i.e., it is The l.a.s.c.s. an s.c.s. mounted in an encapsulation that enables light to reach one or more of its junctions, so that the s.c.s. can be triggered directly by light.

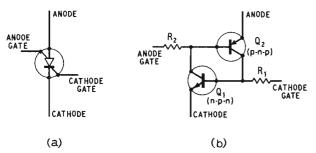

The s.u.s. This device is a Silicon Unilateral Switch, and uses the symbol shown in Figure 1.18a. Figures 1.18b and 1.18c show two alternative equivalent circuits of the device, which is essentially an s.c.r. with

Figure 1.18a. S.U.S. symbol. Figure 1.18b and c. S.U.S. equivalent circuits.

an anode gate (instead of a cathode gate) and with a built-in zener diode between the gate and cathode. Normally the device is used with the gate connection left open. In this case the device acts as a voltage-triggered switch which turns on and saturates as soon as the anode voltage becomes sufficiently positive to cause the internal zener diode to start to break down via the base emitter junction of  $Q_2$ . The typical turn-on voltage of the device is 8 V. The turn-on voltage can be reduced by wiring a lower voltage zener diode between the gate and cathode.

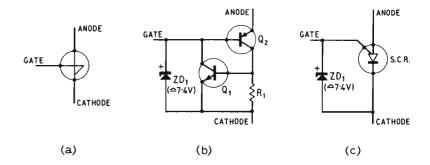

The s.b.s., or Silicon Bilateral Switch, uses the symbol shown in Figure 1.19a. The device consists of two identical s.u.s. structures connected in inverse parallel within a single housing, as indicated by the equivalent circuit of Figure 1.19b. The device acts as a voltagetriggered switch that can be fired by either polarity of voltage.

Figure 1.19a. S.B.S. symbol.

Figure 1.19b. S.B.S. equivalent circuit.

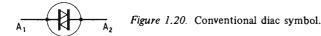

The diac is also a bilateral trigger device, and uses the The diac. symbol shown in Figure 1.20. This symbol in fact gives a slightly misleading impression of the device structure and characteristics, since the trigger diac is not a true thyristor, and uses a special three-layer transistor structure that exhibits a negative resistance characteristic at the firing points.

For most practical purposes, however, the diac can be regarded as an s.b.s. with a high turn-on voltage (about 35 V) and a high saturation voltage (about 30 V). Thus, if a rising voltage is applied to the device via a limiting resistor, the diac acts as an open switch until the applied potential reaches 35 V, at which point the device triggers and develops a 5 V pulse across the load, the remaining 30 V being developed across the diac. The diac turns off when its current falls below a minimum holding value. The device can be connected into circuit in either polarity, and is widely used as a trigger device in phase-triggered triac variable power control applications.

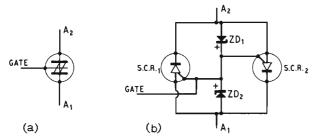

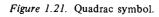

The quadrac. The quadrac is simply a triac with a diac built into its gate network, the two devices being housed in a single package. The quadrac is specifically designed for use in phase-triggered variable power control applications, and uses the symbol shown in Figure 1.21.

The u.j.t. The u.j.t., or Unijunction Transistor, uses the symbol shown in Figure 1.22a. The u.j.t. is a two-layer solid-state trigger device, and is not a true member of the thyristor family. Its characteristics can. however, be simulated by a thyristor equivalent circuit for most practical purposes, as shown in Figures 1.22b and 1.22c. It can be seen that the device resembles an s.c.r. with anode gate triggering provided via a fixed potential divider formed by  $R_1$  and  $R_2$ .

Figure 1.22a. U.J.T. symbol.

Figure 1.22b. Transistor equivalent of the u.j.t.

Figure 1.22c. Alternative equivalent of the u.i.t.

The device is normally wired in circuit so that  $B_2$  is at a fixed positive voltage, and a variable input voltage is applied to E: Due to the voltage divider action of  $R_1$  and  $R_2$  a fixed 'reference' voltage is applied to  $Q_2$ base under this condition. If the input voltage at E is below the reference voltage, therefore, Q<sub>2</sub> s base-emitter junction is reverse biased, and both transistors are cut off. E thus appears as a high impedance to the input signal. If, on the other hand, the voltage at E rises significantly above the reference value set by  $R_1$  and  $R_2$ , the  $Q_2$  base-emitter junction becomes forward biased and the circuit regenerates and switches sharply on. E thus appears as a low impedance under this condition. The voltage at which turn-on occurs is known as the 'peak-point' voltage.

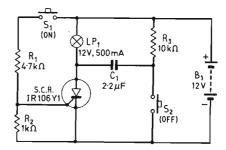

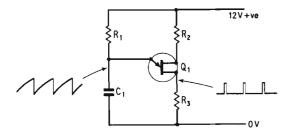

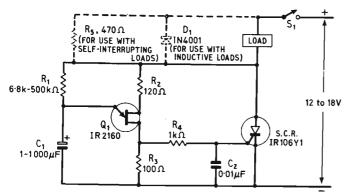

Figure 1.23 shows how the u.j.t. can be wired as a simple relaxation oscillator. When power is first applied to the circuit  $C_1$  is fully discharged and the u.j.t. is off. As soon as power is applied  $C_1$  starts to charge exponentially via  $R_1$ . Eventually, after a pre-set delay, the  $C_1$ voltage rises to the peak-point or firing voltage of the u.j.t, which then fires and discharges  $C_1$  rapidly into  $R_3$  as E goes into a low-impedance saturated state. As the  $C_1$  charge decreases a point is reached where the

#### 22 BASIC PRINCIPLES AND PROJECTS

E current of the u.j.t. falls below the devices minimum holding or 'valley' current, and the device turns off.  $C_1$  then starts to charge again via  $R_1$ , and the process repeats. The circuit thus acts as a free-running oscillator that generates a sawtooth waveform across  $C_1$  and a pulse waveform across  $R_3$ .  $R_2$  is used to enhance the circuits thermal stability.

A very important point about the *Figure 1.23* circuit concerns the selection of the  $R_1$  value. This value must be large enough to ensure

Figure 1.23. Simple u.j.t. relaxation oscillator circuit and waveforms.

that the u.j.t. can turn off once  $C_1$  is discharged, i.e., the maximum  $R_1$  current must be lower than the u.j...s valley current, which is typically about 5 mA. In most cases the minimum  $R_1$  value is restricted to a few thousand ohms. The  $R_1$  value must, on the other hand, be low enough to provide the u.j.t. with adequate turn-on or 'peak-point' triggering current once  $C_1$  reaches the peak-point voltage of the u.j.t. Worst-case peak-point currents are normally of the order of a few microamps, so the maximum  $R_1$  value is usually restricted to a few hundred thousand ohms. Note, therefore, that the  $R_1$  value can be varied over a 100:1 range in this simple circuit, and that the operating frequency or periods of the oscillator can thus be varied over the same range by simply making  $R_1$  a variable control.

#### CHAPTER 2

# 15 A.C. POWER-SWITCHING PROJECTS

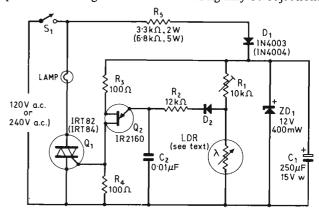

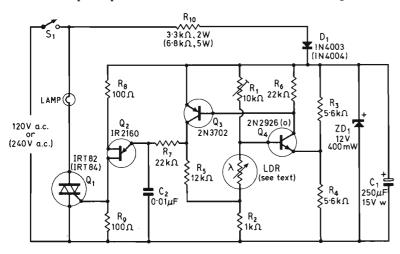

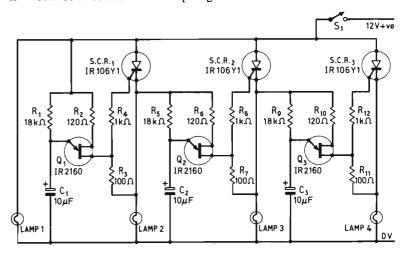

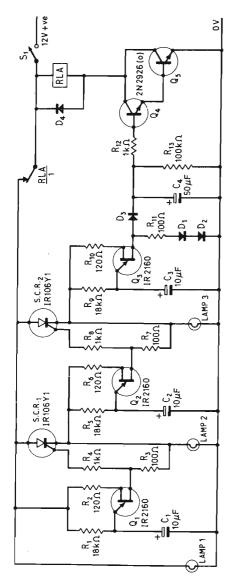

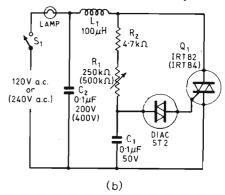

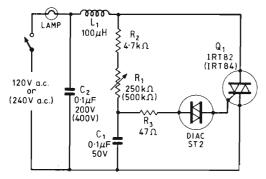

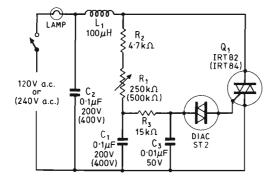

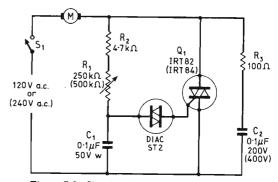

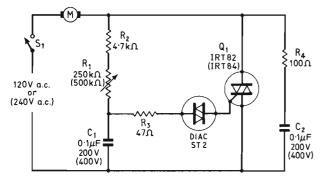

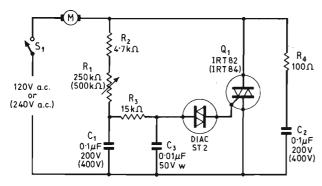

Triacs are high-speed solid-state a.c. power switches. They have no moving parts to arc or wear out, and they give a high power gain between their gate-control and main terminals. They can thus be used with advantage to replace conventional mechanical switches and relays in many power-control applications, and can be made to perform a variety of sophisticated switching tasks.

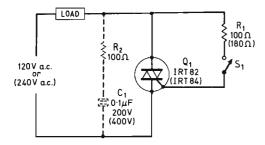

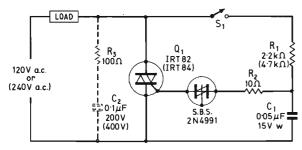

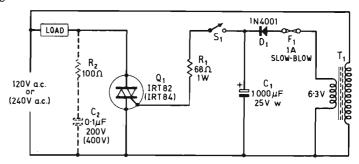

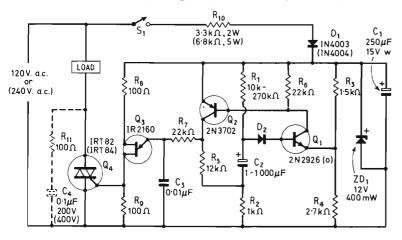

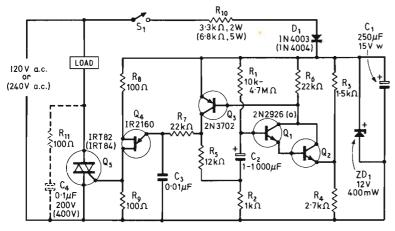

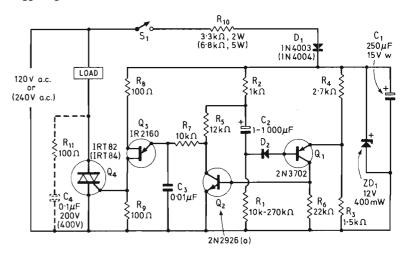

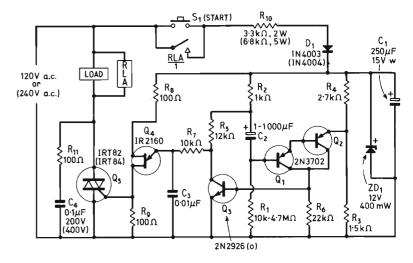

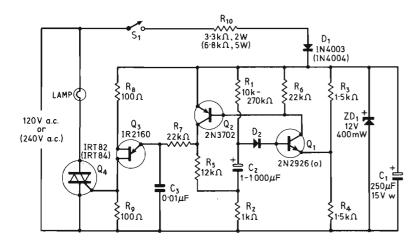

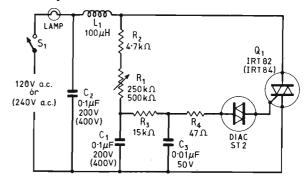

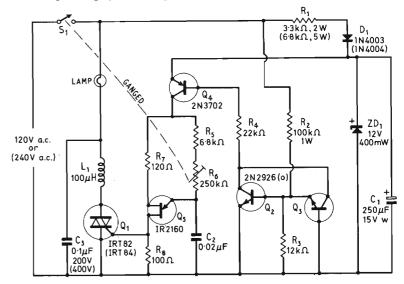

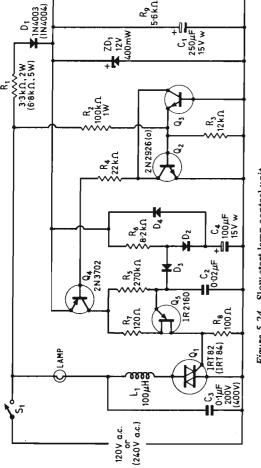

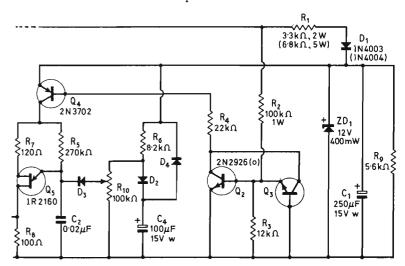

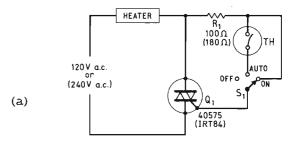

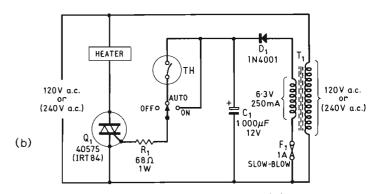

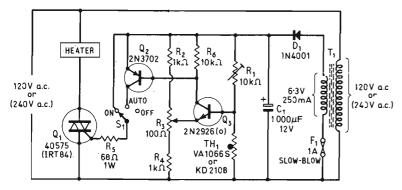

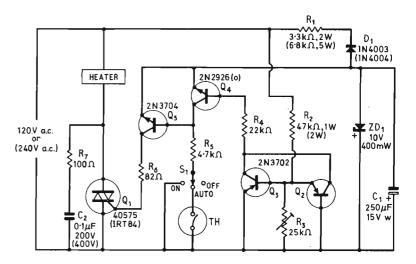

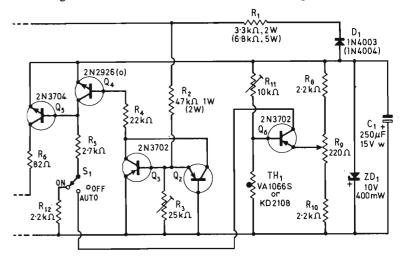

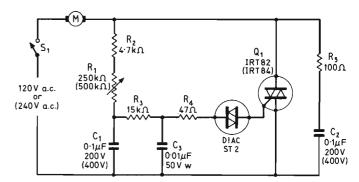

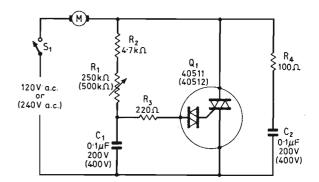

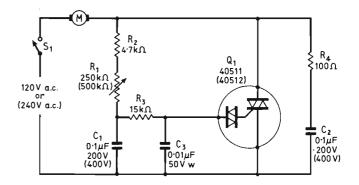

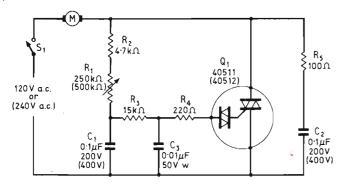

Fifteen a.c. power-switching projects are described in this chapter. They include simple power switches, a self-latching switch, water or steam-operated line switches, synchronous switches, and automatic overload switches. All these projects are designed around the IRT82 or IRT84 triacs manufactured by International Rectifier. The IRT82 is a 200 V 8 A device, and can handle loads up to 960 W on 120 V a.c. lines in all the projects described here: The IRT84 is a 400 V 10 A device, and can handle loads up to 2 400 W on 240 V lines. The triacs must, of course, be fitted to suitable heat sinks when operated at high power levels. Typically, the specified triacs dissipate about 18 W when operating at full load power.

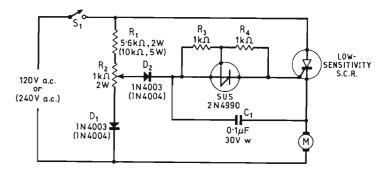

# Simple power-switching projects

Figure 2.1 shows the circuit of a simple line-triggered a.c. power switch. The operation of this circuit has already been described in detail in Chapter 1, and is such that the triac turns on shortly after the start of each half-cycle via  $R_1$  when  $S_1$  is closed. The  $R_1$  gate-drive is removed automatically when the triac turns on, so the mean current through  $S_1$  is of the order of only a few milliamps, although a peak-surge current up to two amps may flow through  $S_1$  at the instant that the switch is first closed.

Figure 2.1. Simple a.c. power switch, line triggered.

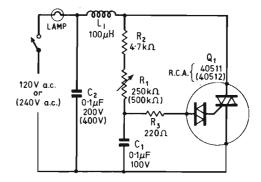

The peak-surge turn-on current of  $S_1$  can be reduced to less than 100 mA by using the circuit shown in Figure 2.2. Here the triac's gate drive is derived from  $R_1 - C_1$  and silicon bilateral switch (s.b.s.). The circuit action is such that  $C_1$  starts to charge up via  $R_1$  at the start of each half cycle, the  $C_1$  voltage following that of the a.c. power line, until  $C_1$  reaches the firing voltage of the s.b.s. (about 8 V). The s.b.s. then fires and discharges  $C_1$  into the gate of the triac via currentlimiting resistor  $R_2$ , thus driving the triac on. As the triac goes on it saturates and removes all power from the gate-drive network. The triac

Figure 2.2. A.C. power switch with s.b.s -aided triggering.

turns off automatically at the end of the half-cycle, and the triggering process then repeats.

Note that the gate trigger current of this circuit is obtained from  $C_1$ rather than  $R_1$ , and that  $R_1$  can thus be given a fairly large value (to limit the peak-surge turn-on current of  $S_1$ ) without causing the triac to turn on excessively late in each half-cycle.

The circuits of Figures 2.1 and 2.2 perform as efficient power switches, but do not turn on in each half-cycle until the line voltage has

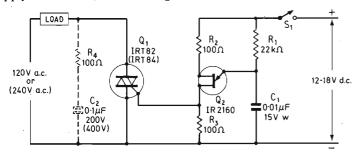

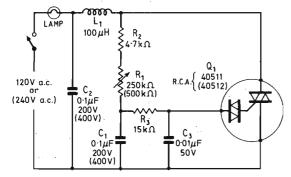

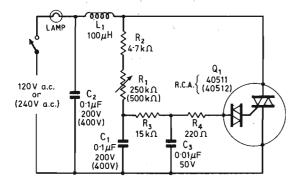

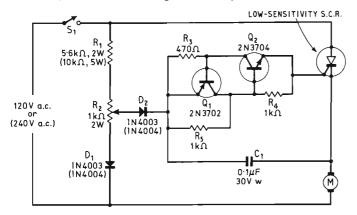

risen to a value of several volts. These circuits thus generate continuous low-level r.f.i. when  $S_1$  is closed, and this r.f.i. may interfere with a.m. radios that are placed close to the triac circuitry. This r.f.i. problem can be overcome by using d.c. triggering of the triac gate, as shown in Figures 2.3 and 2.4.

Figure 2.3. Simple a.c. power switch, d.c. triggered.

The gate drive is taken from the d.c. supply via  $S_1$  and  $R_1$  in the Figure 2.3 circuit, and  $S_1$  passes an on current of about 120 mA. In the Figure 2.4 circuit the gate drive is obtained via switching transistor  $O_2$ . which is driven on via  $S_1$ , and  $S_1$  passes an on current of less than 3 mA.

Figure 2.4. A.C. power switch with transistor-aided d.c. triggering.

The  $S_1$  current can be further reduced by using an additional transistor stage. By replacing  $S_1$  with suitable electronic circuitry the triac can be turned on by heat, light, sound, etc. The d.c. supply in these two circuits can be obtained from batteries, or from the a.c. power line via a suitable step-down transformer and rectifier and smoothing network. as shown in the diagrams.

# 15 A.C. POWER-SWITCHING PROJECTS

The basic circuits of Figures 2.1 and 2.4 can be used with either resistive or inductive loads. If inductive loads are used in these circuits an R-C 'snubber' network must be wired across the triacs, as shown in the diagrams.

# Special power-switching projects

A disadvantage of the d.c. triggered circuits of Figures 2.3 and 2.4 is that they take a fairly heavy current (roughly 120 mA) from the d.c. supply whenever  $S_1$  is closed. Figure 2.5 shows a circuit that overcomes

Figure 2.5. A.C. power switch with u.j.t. triggering.

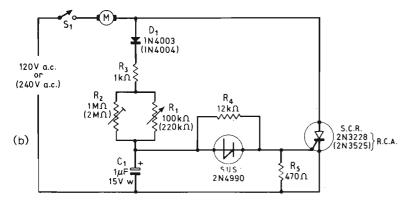

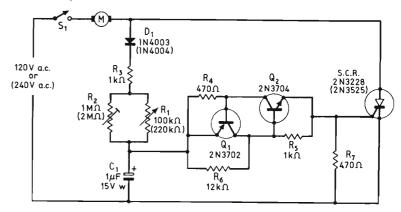

this snag. Here,  $Q_2$  is a free-running unijunction oscillator or pulse generator which feeds a series of high power trigger pulses into the triac gate whenever  $S_1$  is closed. The oscillator operates at a frequency of several kHz, and generates roughly 50 trigger pulses during each halfcycle of the a.c. power line waveform. Consequently, the triac is fired by the first trigger pulse occurring in each half-cycle, and this pulse occurs within a few degrees of the start of the half-cycle. The triac is thus turned on almost permanently when  $S_1$  is closed, and virtually full power is applied to the a.c. load.

The triac is turned on by pulsed (rather than steady) d.c. gate drive, and a considerable saving in gate drive current results. The u.j.t. circuit in fact draws a total current of only 4 mA or so from the d.c. supply. The d.c. supply can be derived from batteries, or from the a.c. power line via a suitable step-down transformer and rectifier and smoothing network.

A simple but very useful development of the Figure 2.5 circuit is shown in Figure 2.6. This circuit is exactly the same as described above, except that the unijunction trigger pulses are fed into the triac gate via an isolating pulse transformer with a 1:1 turns ratio. Consequently, the u.j.t. circuit gives full on-off control of the triac, but is electrically fully isolated from the a.c. power line. The u.j.t. control circuitry can be grounded, for safety, if required.

Figure 2.6. Isolated-input line switch.

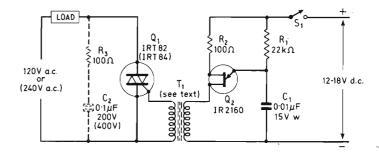

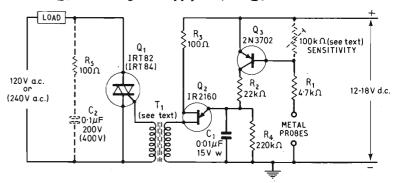

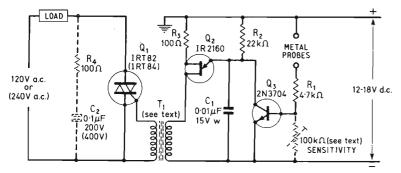

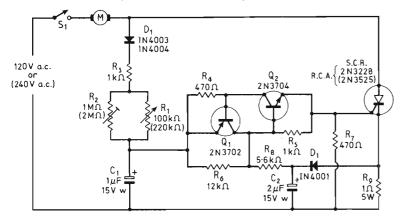

Figure 2.7 shows how the isolated-input line switch can be modified to act as a water or steam-operated line switch that turns on in the presence of moisture.  $O_3$  is wired between the positive d.c. line and  $R_2$ (the u.j.t.s main timing resistor), and  $Q_3$  base is taken to a metal probe via limiting resistor  $R_1$ . When the probes are open zero base drive flows to  $Q_3$ , which thus acts as an open switch. Under this condition the u.j.t. fails to oscillate, and the triac is off. When a resistance less than a few megohms is placed across the probes, on the other hand, base drive flows to  $Q_3$  via the negative supply line, and  $Q_3$  acts like a closed

Figure 2.7. Water or steam-operated line switch (turns on in presence of moisture).

switch. Under this condition the u.j.t. oscillates in the normal way, and the triac turns on. Water and steam have distinct resistive qualities. Consequently, when water or steam come into contact with both metal probes simultaneously the triac turns on, and the circuit acts as a water or steam-operated line switch.

The action of the circuit can be reversed, so that the triac is normally on but turns off in the presence of water or steam, by using the

connections shown in Figure 2.8.  $Q_3$  in this circuit is wired across  $C_1$ . A shunt thus appears across the capacitor when moisture appears across the probes, and the u.j.t. then stops oscillating and the triac turns off. A resistance of less than two megohms must appear across the probes to ensure proper turn-off of the triac.

The sensitivities of the Figure 2, 7 and 2.8 circuits can be reduced to a pre-set level, if required, by wiring a 100 000 ohm pre-set resistor across the base-emitter junction of  $Q_3$ , as shown dotted in the diagrams. One

Figure 2.8. Water or steam-operated line switch (turns off in presence of moisture).

of the two metal probes used in each circuit can be grounded, if required, as is also shown in the diagrams. Transformer  $T_1$  is a pulse transformer with a 1:1 turns ratio. This transformer can be home-made as follows.

Take a length of <sup>3</sup>/<sub>8</sub> in diameter ferrite rod (as used in a.m. radio antennae) and cut off a piece 1 in long. Wind approximately 25 turns of 28 to 30 s.w.g. or a.w.g. insulated copper wire onto the piece to form the primary winding, and then bind in place with a layer of insulating tape. Now place a second 25-turn winding over the insulating tape to form the secondary, and bind this layer in place with another layer of insulating tape. Finally, use an ohmmeter to check that the two windings are properly isolated, and the construction is then complete.

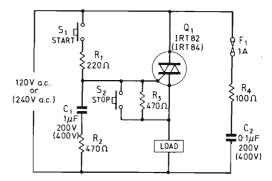

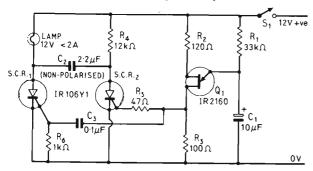

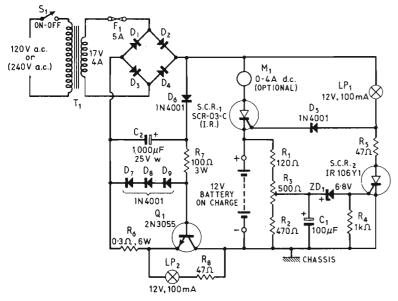

Figure 2.9 shows another special type of power-switching circuit. In this case the circuit acts as a push-button operated self-latching line switch, and operates as follows. Suppose initially that the triac is off. Under this condition zero voltage appears across the load and, since the triac gate is at virtually the same potential as the  $MT_1$  terminal, zero voltage appears on the triac gate or across the  $C_1 - R_2$  network. The triac is thus off,  $C_1$  is discharged, and zero power is developed in the load under this condition.

Suppose now that  $S_1$  is momentarily closed. Under this condition a pulse of gate power is applied to the triac via  $R_1$ , and the triac turns on

and power is applied to the load, causing  $C_1$  to charge and discharge in response to the line voltage via  $R_2$ . The currents of  $C_1$  are, however, close to 90° out of phase with the  $C_1$  voltage. Consequently, when the line voltage falls to zero at the end of the half-cycle the  $C_1$  discharge currents are at a peak value and flow directly into the triac gate and cause the triac to turn on again at the start of the following half-cycle.

Figure 2.9. Push-button operated self-latching line switch.

$R_2$  and  $C_1$  thus cause the triac to self-latch and stay on permanently once the operation has been initiated via  $S_1$ . The circuit can be turned off and reset by briefly closing  $S_2$ , causing  $C_1$  to discharge through the load rather than the triac gate. A snubber network  $(R_4 \text{ and } C_2)$  is wired across the power lines to prevent the triac being turned on by line transients.

# Synchronous power-switching projects

All the projects that we have looked at so far generate a certain amount of r.f.i., either at the moment that power is first applied to the load or continuously so long as power is applied to the load. The magnitude of this r.f.i. is proportional to the magnitude of the instantaneous switching current of the triac, and may be quite objectionable when heavy-current resistive loads such as heaters are used, or when repetitive switching operations are carried out in lamp-flashing or similar applications using resistive loads.

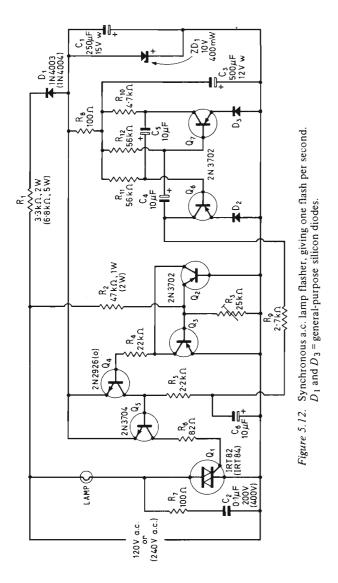

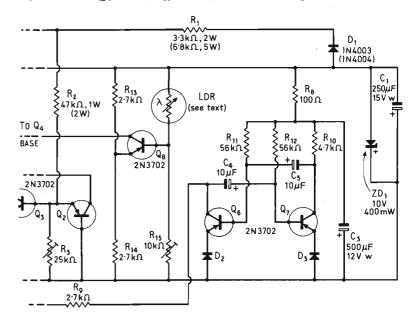

These r.f.i. problems can be completely eliminated by using a synchronous 'zero-voltage' switching technique, in which gate drive is applied to the triac only in the brief periods when the instantaneous line voltage is close to the zero-voltage cross-over points of each halfcycle. Figure 2.10 shows a practical synchronous on-off power switch of this type.

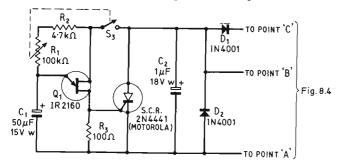

Basically, the circuit contains a line-driven 'zero-crossing' detector section and a d.c.-powered triac-gate-drive section. These two sections are interconnected in such a way that a brief pulse of gate current is applied to the triac only when the line voltage is close to zero in each half-cycle.  $Q_2$  and  $Q_3$  form the zero-crossing detector, and are driven from the a.c. power line by current-limiting potential divider  $R_2 - R_3$ . The  $Q_2 - Q_3$  connection is such that one or other of these transistors is

Figure 2.10. Zero-switching synchronous line switch (turns on with  $S_1$  closed).

driven on whenever the line voltage exceeds a certain 'reference' value (adjustable down to 4.2 V via  $R_3$ ), irrespective of the line voltage polarity, and so that both transistors turn off when the line voltage is below this reference value. The collectors of  $Q_2$  and  $Q_3$  are coupled to the base of  $Q_4$  via  $R_4$ , and  $Q_4$  uses  $R_5$  as its collector load when  $S_1$  is closed.  $R_5$  also provides base drive to  $Q_5$ .  $Q_5$  uses  $R_6$  and the triac gate as its collector load.  $Q_4$  and  $Q_5$  are powered from a zener-regulated d.c. supply derived from the a.c. supply line via  $R_1 - D_1 - ZD_1$  and  $C_1$ .

To understand the circuit action, assume that  $S_1$  is closed and that the instantaneous a.c. line voltage is at some value in excess of the reference value of, say, 5 V. Under this condition either  $Q_2$  or  $Q_3$  is driven on and drives  $Q_4$  to saturation via  $R_4$ .  $Q_4$  has a saturation voltage that is lower than the base-emitter turn-on voltage of  $Q_5$ , so zero base drive flows to  $Q_5$  under this condition, and  $Q_5$  is cut off and zero gate drive is applied to the triac.

Suppose now that the instantaneous line voltage falls below the 5 V reference value, i.e., that the line voltage is very near the zero-voltage

cross-over point near the end of one half-cycle and the start of the next. Under this condition  $Q_2$  and  $Q_3$  both turn off and remove the base drive of  $Q_4$ , which also turns off. Since  $Q_4$  is cut off, heavy base drive flows to  $Q_5$  via  $R_5$ , and  $Q_5$  is driven to saturation. Heavy gate current thus flows into the triac gate via  $Q_5$  and  $R_6$  from the 10 V d.c. supply under this condition, and this current turns the triac on and causes it to self-latch for the duration of the half-cycle. Thus, gate trigger current is applied to the triac only in the brief periods when the line voltage is close to zero at the beginning and end of each half cycle, and negligible r.f.i. is generated under these switching conditions.

Note from the above description of circuit operation that gate drive can be applied to the triac only when base drive is available to  $Q_5$  via  $R_5$ . The triac can thus be turned off or 'inhibited' by removing this base drive. The base drive can be removed in a number of ways. In Figure 2.10 it is removed by wiring on-off switch  $S_1$  in series with  $R_5$ , so the triac in this circuit turns on only when  $S_1$  is closed. In Figure 2.11, on the other hand, it is removed by driving  $Q_4$  permanently on via  $R_4$ , and in this case the triac turns on only when  $S_1$  is open.

Figure 2.11. Zero-switching synchronous line switch (turns on with  $S_1$  open).

The width of the gate pulse of the synchronous switching circuits can be varied via  $R_3$ . The width must be adjusted to ensure that the pulse does not end until the triac main-terminal currents have risen above the holding current in each half-cycle, otherwise the triac will fail to self-latch. To adjust  $R_3$ , connect the selected power load in place, set  $R_3$  to maximum resistance, and apply power to the unit. Now reduce the R<sub>3</sub> value just past the point at which the triac turns on and

applies power to the load. The voltage across  $C_1$  should be checked when  $R_3$  is adjusted, to ensure that it does not fall appreciably below the nominal 10 V value. The adjustment is then complete. If the triac is used with a multi-value load, the above adjustment must be made in the minimum load position only.

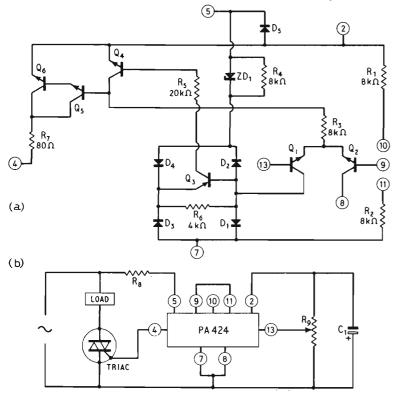

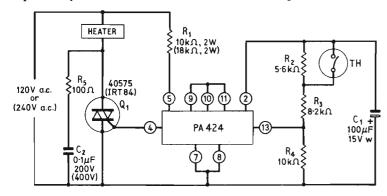

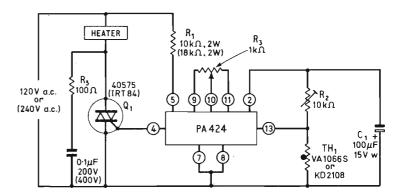

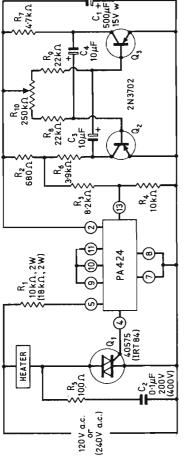

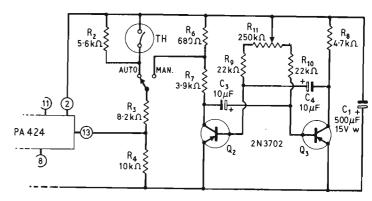

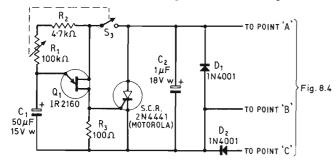

An integrated-circuit version of the synchronous zero-voltage switch is manufactured by General Electric, and is known as the PA424. Figure 2.12a shows the internal circuit of the device, and Figure 2.12b

Figure 2.12a. Internal circuit of the PA424 integrated circuit. Figure 2.12b. Basic connections of the PA424.

shows the basic method of connecting it to a triac. To understand the operation of the device, assume for the moment that  $Q_1 - Q_2 - R_1 R_2 - R_3$  and  $R_9$  do not exist, and imagine that a 16 000 ohm resistor is wired between  $Q_4$  collector and pin 7 of the i.c. Basic circuit operation is as follows.

The a.c. power line is normally connected between pins 5 and 7 of the i.c. via current-limiting resistor  $R_8$ , and an electrolytic smoothing

capacitor is connected between pins 2 and 7. The peak value of the pin 5 alternating voltage is limited to about 10 V by zener diode ZD1 and the series bridge-rectifier network formed by  $D_1$  to  $D_4$ . The pin 5 voltage is rectified by  $D_5$  and smoothed by  $C_1$ , so a stable d.c. supply is developed between pins 2 and 7.  $Q_3$  is wired across the output of the a.c.-powered  $D_1$  to  $D_4$  bridge rectifier in such a way that it is driven on whenever the a.c. line voltage exceeds a few volts.  $Q_3$  and the bridge rectifier thus act as a zero-crossing detector.  $Q_3$  applies base drive to  $\bar{Q}_4$  via  $R_5$  when  $Q_3$ is on, and  $Q_4$  uses the imaginary 16 000 ohm resistor mentioned above as its collector load. This resistor also provides base drive for  $Q_5$  and  $Q_{6}$ . which are connected as a super-alpha pair and provide gate drive to the triac via R<sub>7</sub>.

Thus, when the line voltage is appreciably above the zero-crossing point  $Q_3$  is driven on and drives  $Q_4$  to saturation.  $Q_4$  removes all base drive from  $Q_5$  under this condition, so  $Q_5$  and  $Q_6$  are cut off and zero gate drive is applied to the triac. When, on the other hand, the line voltage is very close to the zero-crossing point of each half-cycle  $Q_3$  is cut off and applying zero base drive to  $Q_4$ , which is also cut off. Heavy base drive is applied to  $Q_5$  via the imaginary 16 000 ohm resistor under this condition, so  $Q_5$  and  $Q_6$  are driven to saturation and heavy gate drive is applied to the triac via  $R_7$ . Thus, gate drive is applied to the triac only in the brief periods when the line voltage is close to the cross-over point in each half-cycle, and r.f.i.-free synchronous operation is obtained. Note at this point that the circuit can be inhibited or turned off by feeding a current into  $Q_3$  base, so that  $Q_3$  is permanently driven on.

Now that the basic operation of the circuit has been examined we can go on to look at the functioning of  $Q_1 - Q_2 - R_1 - R_2 - R_3$  and R<sub>9</sub>. Normally, pins 9, 10 and 11 of the i.c. are shorted together, pin 8 is shorted to pin 7, and pin 13 is taken to a tap on a potential divider  $(R_9)$  that is wired between pins 2 and 8. The  $Q_1 - Q_2$  network thus acts as a differential amplifier, with  $Q_1$  collector current feeding directly into  $Q_3$  base.  $Q_1$  can thus provide an 'inhibit' current to the circuit.

The action of the differential amplifier is such that  $Q_1$  is fully cut off if  $R_9$  is adjusted so that the pin 13 voltage is appreciably negative relative to the fixed voltage that is developed on pin 9 via  $R_1$  and  $R_2$ . Under this condition  $Q_1$  applies zero drive to  $Q_3$ , and the circuit gives synchronous operation of the triac. If, on the other hand,  $R_9$  is adjusted so that pin 13 is positive to pin 9,  $Q_1$  is driven on and passes an inhibit current into  $Q_3$  base. Under this condition zero drive is applied to the triac, which is thus permanently off. A stable potential of roughly half the d.c. supply voltage appears on the emitters of  $Q_1$  and  $Q_2$  under all

conditions. In the PA424, therefore, R<sub>3</sub> is wired between this point and the collector of  $Q_4$ , and serves both as a 'tail' for the differential amplifier and as a collector load resistor for  $Q_4$  (in place of the imaginary 16 000 ohms resistor mentioned earlier).

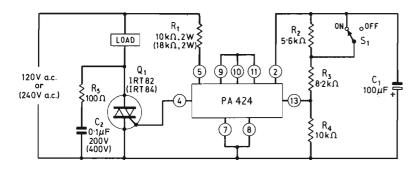

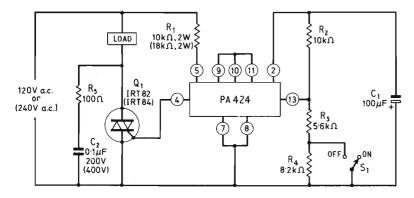

Figures 2.13 and 2.14 show two practical synchronous powerswitching circuits using the PA424. In both cases a potential divider is

Figure 2.13. Zero-switching synchronous line switch using i.c. (turns on with  $S_1$  closed).

wired between pins 2 and 7 so that a fixed voltage is developed on pin 13. This voltage can be shifted, so that the circuit is inhibited, via  $S_1$ . The Figure 2.13 circuit is arranged so that the triac turns on when  $S_1$  is closed, and the Figure 2.14 circuit is arranged so that the triac turns on when  $S_1$  is opened.

Figure 2.14. Zero-switching synchronous line switch using i.c. (turns on with  $S_1$  open).

Note in these circuits that the pulse width of the PA424 is not adjustable, and the triac will thus not self-latch if too low a value of triac load is used. The specified triacs will operate correctly with load powers down to a few hundred watts. If lower power loads are used, triacs with lower holding-current values must be employed.

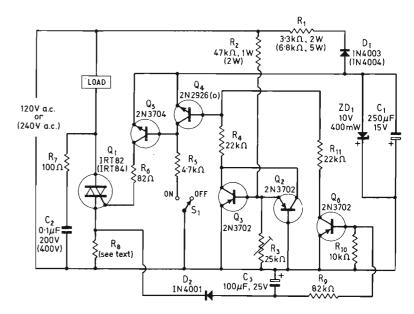

### Automatic overload-switching projects

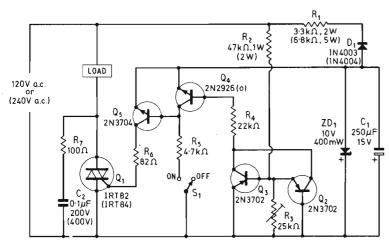

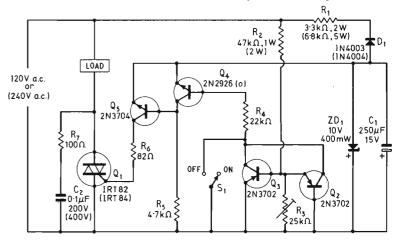

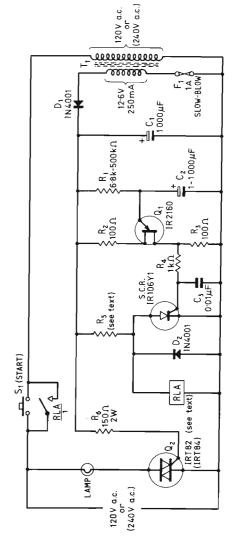

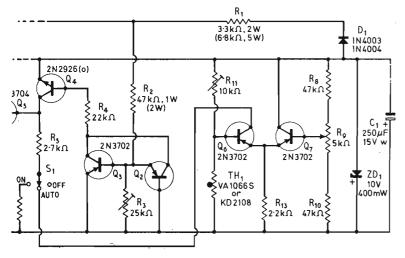

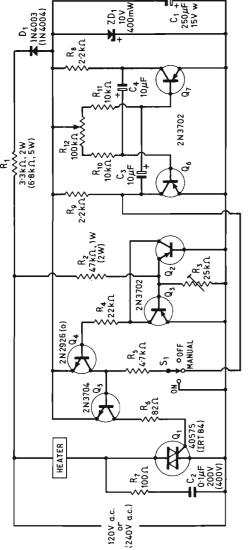

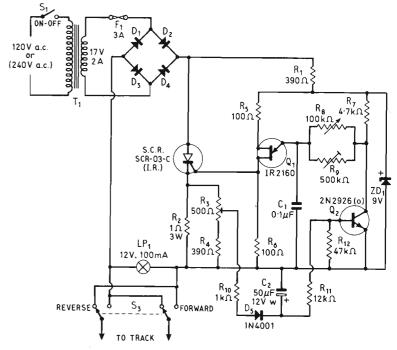

Figures 2.15 and 2.16 show how the synchronous switching circuit of Figure 2.10 can be modified to act as an overload switch that cuts out automatically if the load current rises above a pre-set value. In both circuits a low-value resistor,  $R_8$ , is wired in series with  $MT_1$  of the triac. A voltage proportional to the load current is developed across this resistor, and this voltage is fed to an electronic cut-out on negative half-cycles via  $D_2$ .

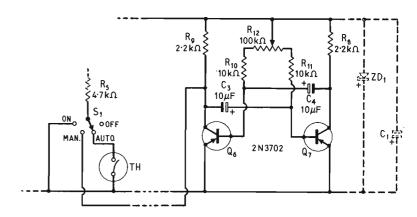

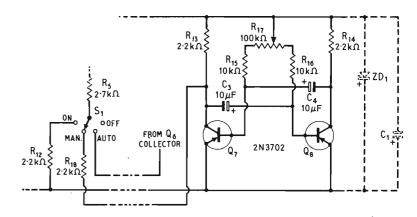

In Figure 2.15 the cut-out comprises  $Q_6 - R_9 - R_{10} - R_{11}$  and  $C_3$ . The circuit action is such that  $C_3$  charges to a voltage proportional to the peak load current on negative half-cycles. If C<sub>3</sub> charges above 5 V  $Q_6$  is driven on via potential divider  $R_9 - R_{10}$ , and  $Q_6$  drives  $Q_4$  on via  $R_{11}$ , thus preventing the triac firing again at the end of the half-cycle.

Figure 2.15. Zero-switching synchronous overload switch, non-latching.

Figure 2.16. Zero-switching synchronous overload switch, self-latching.

The  $C_3$  voltage then slowly decays, and when it falls below 5 V the triac fires again. If the load current is still in excess of the pre-set value the triac again cuts off after applying one or two half-cycles of power.

Thus, this overload switch does not latch into the 'trip' condition when the load current is exceeded, but gives a form of skip-cycling in which test cycles of power are applied to the load at periodic intervals. The period between test cycles is proportional to the magnitude of the overload current, and the r.m.s. power averaged over these periods is of a low order. Full power is applied to the load automatically once the overload is removed. The skip-cycling is not harmful to the triacs specified in this circuit, which have very high overload capabilities. Both triacs can safely handle non-repetitive one-cycle overload currents up to 80 or 100 A.

Figure 2.16 shows how the circuit can be modified to give a latching operation of the overload trip. Here,  $Q_6$  and  $Q_7$  are wired as a regenerative switch that turns on and self-latches when the peak  $R_8$ voltage exceeds 5 V. This switch then removes the triac gate drive via  $R_{12}$  and  $Q_4$ . Once the circuit has tripped it can be reset again by sequentially turning  $S_1$  off and on.

$R_8$  in these two circuits must be chosen so that it develops roughly 5 V at the required peak trip current; e.g., if the circuit is required to trip at 5 A peak, R<sub>8</sub> needs a value of one ohm, and if it is required to trip at 500 mA R<sub>8</sub> needs a value of 10 ohms. If these circuits are to be used with incandescent lamp loads, it should be noted that such lamps pass inrush or turn-on currents several times greater than their normal 'hot' running currents.

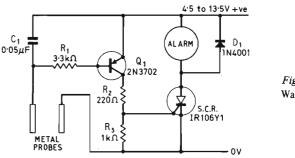

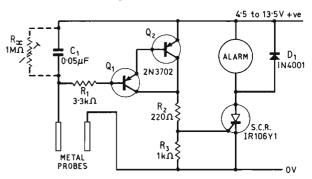

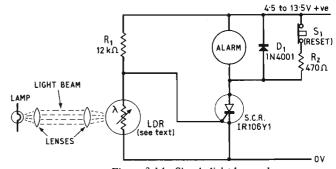

# 20 ELECTRONIC ALARM PROJECTS

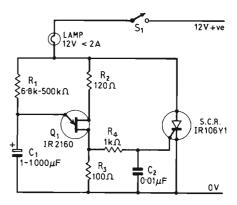

The high power gains, low leakage currents, and high current carrying capacities of s.c.r.s make them ideal for use in a variety of electronic alarm projects. A range of such projects are described in this chapter, and include both simple and advanced burglar alarms, light-beam alarms, smoke alarms, automatic fire alarms, over-temperature alarms, frost alarms, under-temperature alarms, and alarm circuits that are operated by contact with water or steam.

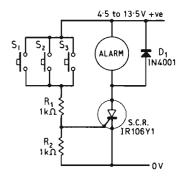

All of these projects are designed around the IR106Y1 s.c.r. manufactured by International Rectifier, and are reasonably versatile circuits. The alarm that each circuit uses can be any self-interrupting bell, buzzer, or siren that draws an operating circuit of less than 2 A. Each circuit must be operated from a battery supply roughly 1.5 V greater than the nominal operating voltage of the alarm device used.

When building these projects, check that the s.c.r. does not get too hot when the alarm is driven on. If it does, connect the s.c.r. heat tab to a heat sink with an area of a couple of square inches or greater.

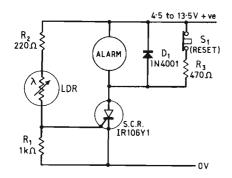

# Contact-operated alarm projects

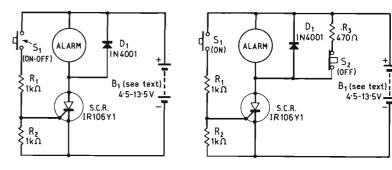

The simplest type of alarm circuit that can be built around the IR106Y1 is the remote-operated alarm shown in Figure 3.1. The circuit is of the non-latching type, and operates when any of the input switches  $(S_1 \text{ to } S_v)$  are closed. Dozens of these switches can be wired in parallel, and each will cause the alarm to operate. These switches pass on currents of only a few milliamps, so they can be placed hundreds of feet away from the s.c.r. and alarm, without risk of trouble from high cable resistance.

Figure 3.1. Remote-operated alarm.

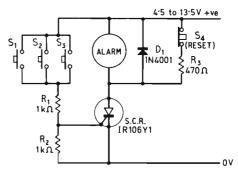

The circuit can be converted to a simple self-latching burglar alarm or a multi-input fire alarm by wiring a latching resistor and reset button across the alarm, as shown in Figure 3.2.

These two circuits have plenty of uses in the home and in industry. They pass typical standby currents of only  $0.1 \mu A$  when the alarm is in the off condition, so cause negligible drain on supply batteries. If the switches are of the microswitch or reed types, the alarms can be made to operate whenever a door or window is opened, or when an object travels beyond a pre-set limit. If the switches are of the pressure-pad type, the alarm can be made to operate whenever a person stands on a

Figure 3.2. Simple make-to-operate burglar alarm, or multi-input fire alarm.

mat or a vehicle passes over a pressure-pad. If thermostat switches are used, the circuits act as automatic fire alarms.

The Figure 3.2. circuit is useful as a burglar alarm, but can be disabled by cutting the cable linking the switches to  $R_1$  or to the positive supply line. A more reliable burglar alarm circuit is that shown in Figure 3.3, which operates and self-latches if any of the switch contacts are briefly operated, or if their connecting leads are cut.

### 40 20 ELECTRONIC ALARM PROJECTS

$C_1$  is a noise-suppressing capacitor, and ensures that the alarm will not be inadvertently operated by the action of switch contacts momentarily bouncing or sliding apart under vibration or shock conditions; the alarm will only operate if the contacts are held open for a period in excess of one millisecond or so.

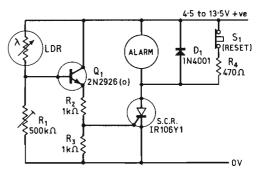

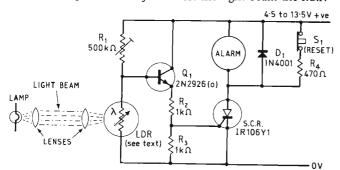

The alarm circuit of Figure 3.3 draws a standby current of 500  $\mu$ A (via  $R_1$ ) when used with a 6 V supply. The standby current can be

Figure 3.3. Break-to-operate burglar alarm. The circuit draws a standby current of 500 µA at 6 V.

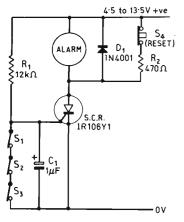

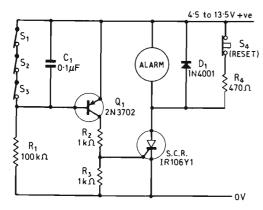

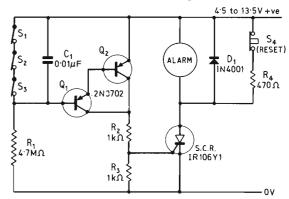

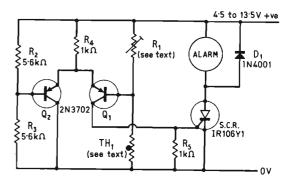

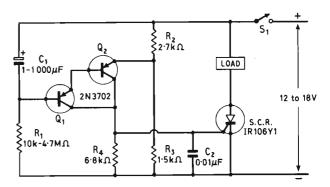

reduced, if required, by increasing the value of  $R_1$  and using a one or two-transistor amplifier to increase the gate sensitivity of the s.c.r., as shown in Figures 3.4 and 3.5. The Figure 3.4 circuit draws a standby current of 60 µA when operated from a 6 V supply, and the Figure 3.5 circuit draws a standby current of 1.4 µA under the same condition.

Figure 3.4 Break-to-operate burglar alarm, drawing a standby current of 60 µA at 6 V.

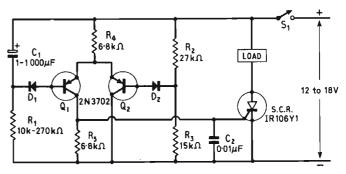

The break-to-operate burglar alarms of Figures 3.3 to 3.5 are far more useful than the simple-make-to-operate type of Figure 3.2, but are still not fully tamper proof. They can be disabled by connecting a jumper lead across the normally closed switch contacts. This snag can be overcome by combining both break-to-operate and make-to-operate

Figure 3.5. Break-to-operate burglar alarm, drawing a standby current of 1.4 µA at 6 V.

switches in a single alarm, as shown in the circuits of Figures 3.6 and 3.7. A burglar is unlikely to know which alarm leads are of the break or make types, and if he cuts or shorts the wrong ones the alarm will instantly sound and self-latch.

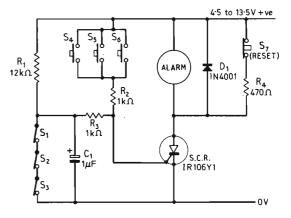

The Figure 3.6 tamper-proof alarm is developed by combining the circuits of Figures 3.2 and 3.3, and draws a standby current of 500 µA

Figure 3.6. Simple 'tamper-proof' burglar alarm, drawing a standby current of 500  $\mu$ A at 6 V.

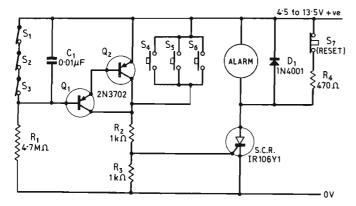

from a 6 V supply. The Figure 3.7 circuit is developed by combining the circuits of Figures 3.2 and 3.5, and draws a standby current of  $1.4 \,\mu\text{A}$  from a 6 V supply.

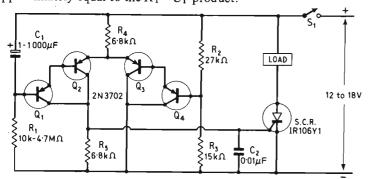

All the burglar alarm circuits looked at so far turn on and self-latch as soon as any of the input switches are operated. Consequently, if the owner turns the alarm on to standby from within a protected building

Figure 3.7. High-performance 'tamper-proof' burglar alarm, drawing a standby current of 1-4  $\mu$ A at 6 V.

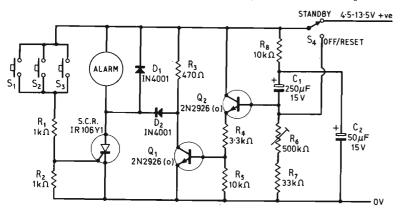

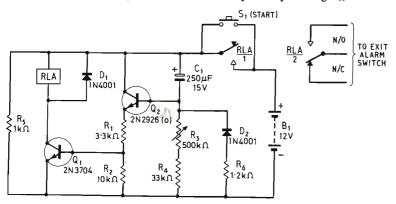

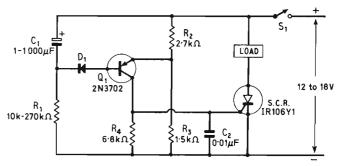

it is impossible for him to leave that building without causing the alarm to operate and self-latch. This snag can be overcome by fitting the alarm with a delayed self-latching facility, which ensures that the alarm does not go into the self-latching mode until some fixed time after the system is initially put into the standby condition. Figure 3.8 shows the practical

Figure 3.8. Simple burglar alarm with delayed self-latching facility giving the owner time to leave a secured building without sounding the alarm.

circuit of a delayed self-latching facility connected up to a simple alarm system of the type shown in Figure 3.2. The facility can, however, be added to any one of the other alarm circuits already described, since the  $D_2 - R_3 - Q_1 - Q_2$  - etc. circuit is used as a time switch that is used to replace the latching resistor and reset button of the earlier circuits.

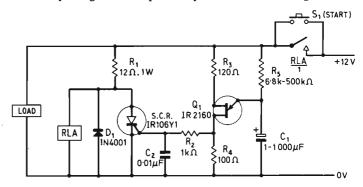

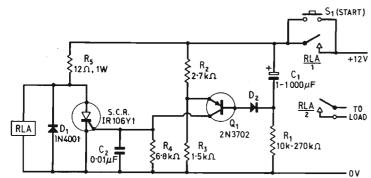

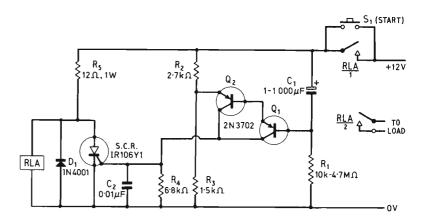

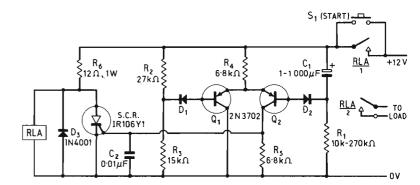

The operation of the *Figure 3.8* circuit is fairly simple.  $C_1$  and  $R_6 - R_7$  form a time-controlled potential divider that is connected to the base of emitter follower  $Q_2$ . The emitter current of  $Q_2$  feeds into the base of common emitter amplifier  $Q_1$ , which uses  $R_3$  as its collector load.  $R_3$  is connected to the s.c.r. anode via  $D_2$ .  $R_8$  and  $C_2$  act as a simple filter network that provides smooth d.c. to the  $C_1$  and  $R_6-R_7$ timing network.

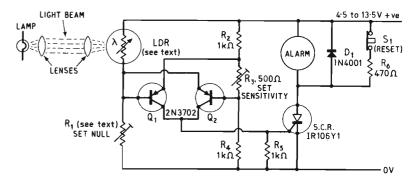

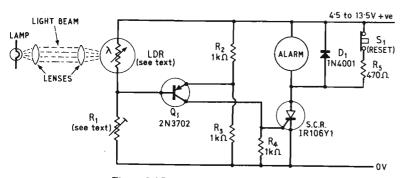

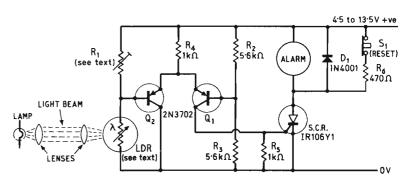

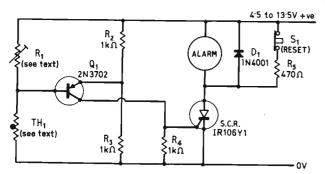

When power is first applied to the circuit by moving  $S_4$  to the standby position  $C_1$  is fully discharged, and  $O_2$  base is thus effectively shorted to the positive supply line. Heavy base drive is thus applied to  $Q_1$  via  $Q_2$ , and  $Q_1$  is driven to saturation. The  $R_3-D_2$  junction is thus effectively shorted to the zero volts line under this condition, so the s.c.r. will not self-latch if any of the input switches are closed at this